# MCIMX28x Linux

**Reference Manual**

All Rights Reserved. No part of this document may be photocopied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means whether, electronic, Mechanical, or otherwise without the prior written permission of Mas electronica. No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law no liability (including liability to any person by reason of negligence) will be accepted by Mas electronica, its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document. Mas electronica reserves the right to change details in this publication without notice. Product and company names herein may be the trademarks of their respective owners.

Mas Elettronica Sas Via Risorgimento 16/C 35030 Selvazzano Dentro (PD) Italy.

## Contents

#### Sommario

| Chapter 1 Introduction                                               |

|----------------------------------------------------------------------|

| Chapter 2 Architecture                                               |

| Chapter 3 Machine Specific Layer (MSL)                               |

| Chapter 4 Direct Memory Access Controller (DMAC) API                 |

| Chapter 5 Persistent Bits Driver                                     |

| Chapter 6 Unique ID on Boot Media43                                  |

| Chapter 7 CPU Frequency Scaling (CPUFREQ) Driver                     |

| Chapter 8 i.MX28 Static Power Management Driver                      |

| Chapter 9 NAND GPMI Flash Driver50                                   |

| Chapter 10 I <sup>2</sup> C Driver                                   |

| Chapter 11 MMC/SD/SDIO Host Driver                                   |

| Chapter 12 Universal Asynchronous Receiver-Transmitter (UART) Driver |

| Chapter 13 USB Driver                                                |

| Chapter 14 Real Time Clock (RTC) Driver                              |

| Chapter 15 Watchdog (WDOG) Driver                                    |

| Chapter 16 External Devices                                          |

| Chapter 17 Board Programming                                         |

| Rohs compliance                                                      |

| Warranty Terms                                                       |

| Contact Informations                                                 |

## **Revision History**

| Rev. | <b>Document</b> Code | Released   | Written      | Verified   | Approved   |

|------|----------------------|------------|--------------|------------|------------|

| 1.0  |                      | 15/07/2014 | N.Convertino | S.Mascetti | S.Mascetti |

|      |                      |            |              |            |            |

|      |                      |            |              |            |            |

|      |                      |            |              |            |            |

#### **About This Book**

The Linux Board Support Package (BSP) represents a porting of the Linux Operating System (OS) to the i.MX processors and its associated reference boards. The BSP supports many hardware features on the platforms and most of the Linux OS features that are not dependent on any specific hardware feature.

#### Audience

This document is targeted to individuals who will port the i.MX Linux BSP to customer-specific products. The audience is expected to have a working knowledge of the Linux 2.6 kernel internals, driver models, and i.MX processors.

#### Conventions

This document uses the following notational conventions:

- •Courier monospaced type indicate commands, command parameters, code examples, and file and directory names.

- •Italic type indicates replaceable command or function parameters.

- •Bold type indicates function names.

#### **Definitions, Acronyms, and Abbreviations**

The following table defines the acronyms and abbreviations used in this document. **Definitions and Acronyms**

| Term                   | Definition                                                                                                                                                               |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC                    | Asynchronous Display Controller                                                                                                                                          |

| address<br>translation | Address conversion from virtual domain to physical domain                                                                                                                |

| API                    | Application Programming Interface                                                                                                                                        |

| ARM®                   | Advanced RISC Machines processor architecture                                                                                                                            |

| AUDMUX                 | Digital audio MUX—provides a programmable interconnection for voice, audio, and synchronous data routing between host serial interfaces and peripheral serial interfaces |

| BCD                    | Binary Coded Decimal                                                                                                                                                     |

| bus                    | A path between several devices through data lines                                                                                                                        |

| bus load               | The percentage of time a bus is busy                                                                                                                                     |

| CODEC                  | Coder/decoder or compression/decompression algorithm—used to encode and decode (or compress and decompress) various types of data                                        |

| CPU                    | Central Processing Unit-generic term used to describe a processing core                                                                                                  |

| Term                   | Definition                                                                                                                                                               |

| CRC        | Cyclic Redundancy Check-Bit error protection method for data communication                                                                                                                                                                                                                                                                     |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CSI        | Camera Sensor Interface                                                                                                                                                                                                                                                                                                                        |  |

| DFS        | Dynamic Frequency Scaling                                                                                                                                                                                                                                                                                                                      |  |

| DMA        | Direct Memory Access-an independent block that can initiate memory-to-memory data transfers                                                                                                                                                                                                                                                    |  |

| DPM        | Dynamic Power Management                                                                                                                                                                                                                                                                                                                       |  |

| DRAM       | Dynamic Random Access Memory                                                                                                                                                                                                                                                                                                                   |  |

| DVFS       | Dynamic Voltage Frequency Scaling                                                                                                                                                                                                                                                                                                              |  |

| EMI        | External Memory Interface—controls all IC external memory accesses (read/write/erase/program) from all the masters in the system                                                                                                                                                                                                               |  |

| Endian     | Refers to byte ordering of data in memory. Little endian means that the least significant byte of the data is stored in a lower address than the most significant byte. In big endian, the order of the bytes is reversed                                                                                                                      |  |

| EPIT       | Enhanced Periodic Interrupt Timer—a 32-bit set and forget timer capable of providing precise interrupts at regular intervals with minimal processor intervention                                                                                                                                                                               |  |

| FCS        | Frame Checker Sequence                                                                                                                                                                                                                                                                                                                         |  |

| FIFO       | First In First Out                                                                                                                                                                                                                                                                                                                             |  |

| FIPS       | Federal Information Processing Standards—United States Government technical standards published by the National Institute of Standards and Technology (NIST). NIST develops FIPS when there are compelling Federal government requirements such as for security and interoperability but no acceptable industry standards                      |  |

| FIPS-140   | Security requirements for cryptographic modules—Federal Information Processing Standard 140-2(FIPS 140-2) is a standard that describes US Federal government requirements that IT products should meet for Sensitive, but Unclassified (SBU) use                                                                                               |  |

| Flash      | A non-volatile storage device similar to EEPROM, where erasing can be done only in blocks or the entire chip.                                                                                                                                                                                                                                  |  |

| Flash path | Path within ROM bootstrap pointing to an executable Flash application                                                                                                                                                                                                                                                                          |  |

| Flush      | Procedure to reach cache coherency. Refers to removing a data line from cache. This process includes cleaning the line, invalidating its VBR and resetting the tag valid indicator. The flush is triggered by a software command                                                                                                               |  |

| GPIO       | General Purpose Input/Output                                                                                                                                                                                                                                                                                                                   |  |

| hash       | Hash values are produced to access secure data. A hash value (or simply hash), also called a message digest, is a number generated from a string of text. The hash is substantially smaller than the text itself, and is generated by a formula in such a way that it is extremely unlikely that some other text produces the same hash value. |  |

| I/O        | Input/Output                                                                                                                                                                                                                                                                                                                                   |  |

| ICE        | In-Circuit Emulation                                                                                                                                                                                                                                                                                                                           |  |

| IP         | Intellectual Property                                                                                                                                                                                                                                                                                                                          |  |

| IPU        | Image Processing Unit —supports video and graphics processing functions and provides an interface to video/still image sensors and displays                                                                                                                                                                                                    |  |

| IrDA       | Infrared Data Association—a nonprofit organization whose goal is to develop globally adopted specifications for infrared wireless communication                                                                                                                                                                                                |  |

| ISR        | Interrupt Service Routine                                                                                                                                                                                                                                                                                                                      |  |

| Term       | Definition                                                                                                                                                                                                                                                                                                                                     |  |

| JTAG       | JTAG (IEEE Standard 1149.1) A standard specifying how to control and monitor the pins of compliant devices on a printed circuit board                                                                                                                                                                                                          |  |

| Kill       | Abort a memory access                                                                                                                                                                                                                                                                                                                          |  |

| КРР        | KeyPad Port—16-bit peripheral used as a keypad matrix interface or as general purpose input/output (I/O)                                                                                                                                                                                                                                       |  |

| line       | Refers to a unit of information in the cache that is associated with a tag                                                                                                                                                                                                                                                                     |  |

| LRU                 | Least Recently Used—a policy for line replacement in the cache                                                                                                                                                                                                                                                                                                          |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MMU                 | Memory Management Unit-a component responsible for memory protection and address translation                                                                                                                                                                                                                                                                            |  |

| MPEG                | Moving Picture Experts Group—an ISO committee that generates standards for digital video compression and audio. It is also the name of the algorithms used to compress moving pictures and video                                                                                                                                                                        |  |

| MPEG<br>standards   | Several standards of compression for moving pictures and video:<br>•MPEG-1 is optimized for CD-ROM and is the basis for MP3<br>•MPEG-2 is defined for broadcast video in applications such as digital television set-top boxes and DVD • MPEG-3 was merged into MPEG-2<br>•MPEG-4 is a standard for low-bandwidth video telephony and multimedia on the World-Wide Web  |  |

| MQSPI               | Multiple Queue Serial Peripheral Interface—used to perform serial programming operations necessary to configure radio subsystems and selected peripherals                                                                                                                                                                                                               |  |

| MSHC                | Memory Stick Host Controller                                                                                                                                                                                                                                                                                                                                            |  |

| NAND Flash          | Flash ROM technology—NAND Flash architecture is one of two flash technologies (the other being NOR) used in memory cards such as the Compact Flash cards. NAND is best suited to flash devices requiring high capacity data storage. NAND flash devices offer storage space up to 512-Mbyte and offers faster erase, write, and read capabilities over NOR architecture |  |

| NOR Flash           | See NAND Flash                                                                                                                                                                                                                                                                                                                                                          |  |

| PCMCIA              | Personal Computer Memory Card International Association—a multi-company organization that has developed a standard for small, credit card-sized devices, called PC Cards. There are three types of PCMCIA cards that have the same rectangular size (85.6 by 54 millimeters), but different widths                                                                      |  |

| physical<br>address | The address by which the memory in the system is physically accessed                                                                                                                                                                                                                                                                                                    |  |

| PLL                 | Phase Locked Loop—an electronic circuit controlling an oscillator so that it maintains a constant phase angle ( a lock) on the frequency of an input, or reference, signal                                                                                                                                                                                              |  |

| RAM                 | Random Access Memory                                                                                                                                                                                                                                                                                                                                                    |  |

| RAM path            | Path within ROM bootstrap leading to the downloading and the execution of a RAM application                                                                                                                                                                                                                                                                             |  |

| RGB                 | The RGB color model is based on the additive model in which Red, Green, and Blue light are combined to create other colors. The abbreviation RGB comes from the three primary colors in additive light models                                                                                                                                                           |  |

| RGBA                | RGBA color space stands for Red Green Blue Alpha. The alpha channel is the transparency channel, and is unique to this color space. RGBA, like RGB, is an additive color space, so the more of a color placed, the lighter the picture gets. PNG is the best known image format that uses the RGBA color space                                                          |  |

| RNGA                | Random Number Generator Accelerator—a security hardware module that produces 32-bit pseudo random numbers as part of the security module                                                                                                                                                                                                                                |  |

| ROM                 | Read Only Memory                                                                                                                                                                                                                                                                                                                                                        |  |

| Term                | Definition                                                                                                                                                                                                                                                                                                                                                              |  |

| ROM<br>bootstrap    | Internal boot code encompassing the main boot flow as well as exception vectors                                                                                                                                                                                                                                                                                         |  |

| RTIC                | Real-Time Integrity Checker—a security hardware module                                                                                                                                                                                                                                                                                                                  |  |

| SCC                 | SeCurity Controller—a security hardware module                                                                                                                                                                                                                                                                                                                          |  |

| SDMA                | Smart Direct Memory Access                                                                                                                                                                                                                                                                                                                                              |  |

| SDRAM               | Synchronous Dynamic Random Access Memory                                                                                                                                                                                                                                                                                                                                |  |

| SoC                 | System on a Chip                                                                                                                                                                                                                                                                                                                                                        |  |

| SPBA                | Shared Peripheral Bus Arbiter-a three-to-one IP-Bus arbiter, with a resource-locking mechanism                                                                                                                                                                                                                                                                          |  |

| SPI                 | Serial Peripheral Interface—a full-duplex synchronous serial interface for connecting low-/medium-bandwidth external devices using four wires. SPI devices communicate using a master/slave relationship over two data lines                                                                                                                                            |  |

|        | and two control lines: Also see SS, SCLK, MISO, and MOSI                                                                                                                                                                                                                                                                                                                                         |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SRAM   | Static Random Access Memory                                                                                                                                                                                                                                                                                                                                                                      |  |

| SSI    | Synchronous-Serial Interface-standardized interface for serial data transfer                                                                                                                                                                                                                                                                                                                     |  |

| TBD    | To Be Determined                                                                                                                                                                                                                                                                                                                                                                                 |  |

| UART   | Universal Asynchronous Receiver/Transmitter-asynchronous serial communication to external devices                                                                                                                                                                                                                                                                                                |  |

| UID    | Unique ID-a field in the processor and CSF identifying a device or group of devices                                                                                                                                                                                                                                                                                                              |  |

| USB    | SB Universal Serial Bus—an external bus standard that supports high speed data transfers. The USB 1.1 specification supports data transfer rates of up to 12 Mb/s and USB 2.0 has a maximum transfer rate of 480 Mbps. A single USB port can be used to connect up to 127 peripheral devices, such as mice, modems, and keyboards. USB also support: Plug-and-Play installation and hot plugging |  |

| USBOTG | USB On The Go—an extension of the USB 2.0 specification for connecting peripheral devices to each other.<br>USBOTG devices, also known as dual-role peripherals, can act as limited hosts or peripherals themselves depending<br>on how the cables are connected to the devices, and they also can connect to a host PC                                                                          |  |

| word   | A group of bits comprising 32-bits                                                                                                                                                                                                                                                                                                                                                               |  |

## **Suggested Reading**

The following documents contain information that supplements this guide

## Chapter 1 Introduction

The i.MX family Linux Board Support Package (BSP) supports the Linux Operating System (OS) on the following processor:

i.MX28 Applications Processor

The purpose of this software package is to support Linux on the i.MX family of Integrated Circuits (ICs) and their associated platforms (EVK). It provides the necessary software to interface the standard open-source Linux kernel to the i.MX hardware. The goal is to enable Freescale customers to rapidly build products based on i.MX devices that use the Linux OS.

The BSP is not a platform or product reference implementation. It does not contain all of the product- specific drivers, hardware-independent software stacks, Graphical User Interface (GUI) components, Java Virtual Machine (JVM), and applications required for a product. Some of these are made available in their original open-source form as part of the base kernel.

The BSP is not intended to be used for silicon verification. While it can play a role in this, the BSP functionality and the tests run on the BSP do not have sufficient coverage to replace traditional silicon verification test suites.

### 1.1 Software Base

The i.MX BSP is based on version 2.6.35.3 of the Linux kernel from the official Linux kernel web site (<u>http://www.kernel.org</u>). It is enhanced with the features provided by Freescale.

#### 1.2 Features

Table 1-1 describes the features supported by the Linux BSP for specific platforms.

| Feature                   | Description                                                                                                                                                                                         | Chapter Source                  | Applicable<br>Platform |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------|

| Machine<br>Specific Layer |                                                                                                                                                                                                     |                                 |                        |

| MSL                       | Machine Specific Layer (MSL) supports interrupts, Timer, Memory Map, GPIO/IOMUX, SPBA, SDMA.                                                                                                        | Chapter 3, "Machine<br>Specific | All                    |

|                           | •Interrupts (AITC/AVIC): The Linux kernel contains common ARM code for handling interrupts. The MSL contains platform-specific implementations of functions for interfacing the Linux kernel to the | Layer (MSL)"                    |                        |

|      | <ul> <li>interrupt controller.</li> <li>Timer (GPT): The General Purpose Timer (GPT) is set up to generate an interrupt as programmed to provide OS ticks. Linux facilitates timer use through various functions for timing delays, measurement, events, alarms, high resolution timer features, and so on. Linux defines the MSL timer API required for the OS-tick timer and does not expose it beyond the kernel tick implementation.</li> <li>GPIO/EDIO/IOMUX: The GPIO and EDIO components in the MSL provide an abstraction layer between the various drivers and the configuration and utilization of the system, including GPIO, IOMUX, and external board I/O. The IO software module is board-specific, and resides in the MSL layer as a self-contained set of files. I/O configuration changes are centralized in the GPIO module so that changes are not required in the various drivers.</li> <li>SPBA: The Shared Peripheral Bus Arbiter (SPBA) provides an arbitration mechanism among multiple masters to allow access to the shared peripherals. The SPBA implementation under MSL defines the API to allow different masters to take or release ownership of a shared peripheral.</li> </ul> |                                                               |        |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------|

| DMAC | Both AHB-to-APBH and AHB-to-APBX DMA support configurable DMA descript chain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chapter 4, "Direct<br>Memory Access<br>Controller (DMAC) API" | i.MX28 |

/

ELET

TRO

| Power Management Drivers    |                                                                                                                                                                                                                                                                                                     |                                                          |        |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------|--|

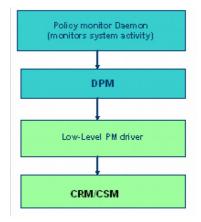

| Low-level PM<br>Drivers     | The low-level power management driver is responsible for<br>implementing hardware-specific operations to meet power<br>requirements and also to conserve power on the development<br>platforms. Driver implementations are often different for different<br>platforms. It is used by the DPM layer. | Chapter 8, "i.MX28 Static<br>Power<br>Management Driver" | i.MX28 |  |

| CPU<br>Frequency<br>Scaling | The CPU frequency scaling device driver allows the clock speed of<br>the CPUs to be changed on the fly.                                                                                                                                                                                             | Chapter 7, "CPU Frequency<br>Scaling (CPUFREQ) Driver"   | i.MX28 |  |

|          | Memory Drivers                                                  |                         |  |

|----------|-----------------------------------------------------------------|-------------------------|--|

| NAND MTD | The NAND MTD driver interfaces with the integrated NAND         | Chapter 14, "NAND Flash |  |

|          | controller. It can support various file systems, such as UBIFS, | Driver                  |  |

|          | CRAMFS and JFFS2. The driver implementation supports the        |                         |  |

|          | lowest level operations on the external NAND Flash chip, such   |                         |  |

| as block read, block write and block erase as the NAND Flash       |

|--------------------------------------------------------------------|

| technology only supports block access. Because blocks in a         |

| NAND Flash are not guaranteed to be good, the NAND MTD             |

| driver is also able to detect bad blocks and feed that information |

| to the upper layer to handle bad block management.                 |

/

ELET

TRO

'n

|                          | <b>Bus Drivers</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                   |          |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------|

| I <sup>2</sup> C         | The I <sup>2</sup> C bus driver is a low-level interface that is used to interface with the I <sup>2</sup> C bus. This driver is invoked by the I <sup>2</sup> C chip driver; it is not exposed to the user space. The standard Linux kernel contains a core I <sup>2</sup> C module that is used by the chip driver to access the bus driver to transfer data over the I <sup>2</sup> C bus. This bus driver supports:<br>•Compatibility with the I <sup>2</sup> C bus standard | Chapter 19, "Inter-IC<br>(I2C) Driver"            | i.MX28   |

|                          | •Bit rates up to 400 Kbps                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                   |          |

|                          | •Standard I <sup>2</sup> C master mode                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                   |          |

|                          | •Power management features by suspending and resuming I <sup>2</sup> C.                                                                                                                                                                                                                                                                                                                                                                                                          |                                                   |          |

| CSPI                     | The low-level Configurable Serial Peripheral Interface (CSPI) driver<br>interfaces a custom, kernel-space API to both CSPI modules. It supports<br>the following features:                                                                                                                                                                                                                                                                                                       | Chapter 21, "SPI Bus<br>Driver"                   | i.MX28   |

|                          | •Interrupt-driven transmit/receive of SPI frames                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                   |          |

|                          | •Multi-client management                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                   |          |

|                          | <ul><li>Priority management between clients</li><li>SPI device configuration per client</li></ul>                                                                                                                                                                                                                                                                                                                                                                                |                                                   |          |

| MMC/SD/S                 | The MMC/SD/SDIO Host driver is implemented using the i.MX28 SSP                                                                                                                                                                                                                                                                                                                                                                                                                  | Chapter 22,                                       | i.MX28   |

| DIO -                    | component, which supports SD/MMC mode.                                                                                                                                                                                                                                                                                                                                                                                                                                           | "MMC/SD/SDIO Host                                 | 1.101A20 |

| SDHC                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Driver"                                           |          |

|                          | UART Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |          |

| Debug and<br>Application | These are three serial UARTs. One that has no DMA support and is intended to work as a debug console (debug UART), and two are high-performance UARTs,                                                                                                                                                                                                                                                                                                                           | Chapter 23, "Universal<br>Asynchronous            | i.MX28   |

| UARTs                    | which are intended to be used by applications (application UART, appUART).                                                                                                                                                                                                                                                                                                                                                                                                       | Receiver-Transmitter<br>(UART)<br>Driver"         |          |

|                          | General Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                   |          |

| USB                      | The USB driver implements a standard Linux driver interface to the ARC USB-OTG controller.                                                                                                                                                                                                                                                                                                                                                                                       | Chapter 24, "ARC USB<br>Driver"                   | i.MX28   |

| RTC                      | This is the integrated Real Time Clock (RTC) module. The RTC is used to keep the time and date while the system is turned off. Additionally, it provides the PIE (periodic interrupt at a specific frequency) and AIE (wake up the system by providing an alarm) features.                                                                                                                                                                                                       | Chapter 25, "Real Time<br>Clock<br>( RTC) Driver" | i.MX28   |

| WatchDog                 | <ul> <li>The Watchdog Timer module protects against system failures by providing an escape from unexpected hang or infinite loop situations or programming errors. This WDOG implements the following features:</li> <li>Generates a reset signal if it is enabled but not serviced within a predefined time-out value</li> </ul>                                                                                                                                                | Chapter 26, "Watchdog<br>(WDOG)<br>Driver"        | i.MX28   |

|                          | •Does not generate a reset signal if it is serviced within a predefined time-<br>out value                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |          |

| Bootloaders |                                      |                      |        |  |  |

|-------------|--------------------------------------|----------------------|--------|--|--|

| uBoot       | uBoot is an open source boot loader. | See uBoot User guide | i.MX28 |  |  |

## Chapter 2 Architecture

This chapter describes the overall architecture of the Linux port to the i.MX processor. The BSP supports all platforms in a single development environment, but not every driver is supported by all processors. Drivers that are common to all platforms are referred as i.MX drivers and drivers unique to a specific platform are referred by the platform name.

TRONCE

## 2.1 Linux BSP Block Diagram

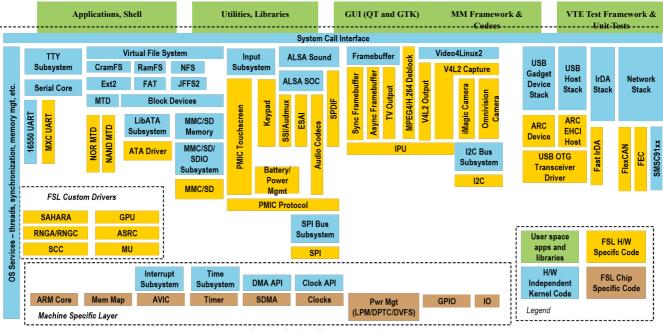

Figure 2-1 shows the architecture of the BSP for the i.MX family of processors. It consists of user space executables, standard kernel components that come from the Linux community, and hardware-specific drivers and functions provided by Freescale for the i.MX processors.

Figure 2-1. BSP Block Diagram

## 2.2 Kernel

The i.MX Linux port is based on the standard Linux kernel. The kernel supports most of the features available in many modern embedded OSs such as:

- •Process and thread management

- •Memory management (memory mapping, allocation/deallocation, MMU, and L1/L2 cache control)

- •Resource management (interrupts)

- •Power management

File systems (VFS, cramfs, ext2, ramfs, NFS, devfs, JFFS2, FAT, UBIFS)

Linux Device Driver model

Standardized APIs

Networking stacks

ARM Linux Kernel customization to support each platform includes a custom kernel configuration and MSL implementation.

#### 2.2.1 Kernel Configuration

For this BSP release, kernel configuration is performed through the Linux Target Image Builder (LTIB). See the *LTIB* documentation for details. The configuration settings available on some platforms that are different from the standard features are as follows:

- •Embedded mode

- •Module loading/unloading

- •ARM9

- •Supported file formats: ELF binaries, a.out, and ECOFF

•Block devices: Loopback, Ramdisk

- •i.MX internal UART

- •File systems: ext2, dev, proc, sysfs, cramfs, ramfs, JFFS2, FAT, pramfs

- •Frame buffer

- •Kernel debugging

- •Automatic kernel module loading

- •Power management

- •Memory Technology Device (MTD) support

- •USB Host/device multiplexing

- •Unsorted Block Images (UBI) support

- •Flash Translation Layer (FTL)

- •CPU frequency scaling

#### 2.2.2 Machine Specific Layer (MSL)

The MSL provides a machine-dependent implementation as required by the Linux kernel, such as memory map, interrupt, and timer. Each ARM platform has its own MSL directory under the arch/arm directory as listed in Table 2-1.

#### Table 2-1. MSL Directories

| Platform | Directory                                                |

|----------|----------------------------------------------------------|

| i.MX28   | <ltib_dir>/rpm/BUILD/linux/arch/arm/mach-mx28</ltib_dir> |

|          |                                                          |

See Chapter 4, "Machine Specific Layer (MSL)," for more information.

#### 2.2.2.1 Memory Map

Before the kernel starts running in the virtual space, the physical-to-virtual address mapping for the I/O peripherals needs to be provided for the MMU to do the translation for memory/register accesses. The mapping is performed through a table structure in the MSL, specific to a particular platform, with each entry specifying a peripheral starting address of virtual addresses, starting address of physical addresses, and the size of the memory region and the type of the region.

#### 2.2.2.2 Interrupts

The standard Linux kernel contains common ARM code for handling interrupts. The MSL contains platform-specific implementations of functions for interfacing the Linux kernel to the ARM9 Interrupt Controller (AITC).

Together, they support the following capabilities:

- •AVIC initialization

- •ARM Interrupt Controller (AITC) initialization

- •Interrupt enable/disable control

- •ISR binding

- •ISR dispatch

- •Interrupt chaining

- •Standard Linux API for accessing interrupt functions

#### 2.2.2.3 General Purpose Timer (GPT)

The GPT is configured to generate an interrupt every 10 ms to provide OS ticks. This timer is also used by the kernel for additional timer events. Linux defines the MSL timer API required for the OS-tick timer and does not expose it beyond the kernel tick implementation. Linux facilitates timer use through various functions for timing delays, measurement, events, and alarms. The GPT is also used as the source to support the high resolution timer feature. The timer tick interrupt is disabled in low-power modes other than idle.

#### 2.2.2.4DMA API

The i.MX28 device is equipped with two AHB-to-APBH/AHB-to-APBX bridges with builtin DMA capability that allow programmed data transfers between SDRAM and peripheral devices. The DMA is abstracted as a number of channels dedicated to on-chip peripheral devices such as UART, DAC/ADC, GPMI and so on. Each DMA channel is programmed by a set of per-channel registers and special DMA command structure located in memory. A command describes a single DMA transaction and may be chained with other commands. The MSL implements an internal DMA API that allows other drivers to initialize DMA channels and control DMA transfers. The following features are implemented:

- •Command structures allocation/de-allocation

- •Channel initialization

- •Channel execution control: start/stop/freeze a channel

•Channel interrupts control

## 2.2.2.5 Input/Output (I/O)

The Input/Output (I/O) component in the MSL provides an abstraction layer between the various drivers and the configuration and utilization of the system, including GPIO, IOMUX, pin multiplexing, and external board I/O. The I/O software module is board-specific and resides in the MSL layer as a self-contained set of files. It provides the following features as part of a custom kernel-space API:

- •Initialization for the default I/O configuration after boot

- •Functions for configuring the various I/O for active use

- •Functions for configuring the various I/O for low power mode

- •Functions for controlling and sampling GPIO and board I/O

- •Functions for enabling, disabling, and binding callback functions to GPIO and EDIO interrupts

- •Functions to support different priority levels during ISR registration for different modules; if more than one interrupt occurs at the same time, the higher priority ISR callback gets called first

- •Atomic helper functions for GPIO, EDIO, and IOMUX configuration

These functions are organized by functional usage, and not by pin or port. This allows I/O configuration changes to be centralized in the GPIO module without requiring changes in the various drivers. These functions are used by other device drivers in the kernel space. User level programs do not have access to the functions in the GPIO module.

The exact API and implementations are different on each platform to account for the differences in hardware, drivers, and boards. This module is an evolving module. As more drivers are added, more functions are required from this module. The additions to the module are included in every new release of the BSP.

## 2.2.2.6 Pin Multiplexing

The pin multiplexing component is responsible for setting I/O pin configuration and routing. Each I/O pin is shared between up to three different i.MX28 modules or can be configured as a GPIO pin and controlled by software. The MSL implements a kernel-space API used by the MSL board specific components to set pins configurations corresponding to a particular board. The following features are implemented: • Pin resource manager to avoid conflicts on pin use

- •Pin voltage control

- •Pin strength control

- •Pin pull-up resistor control

- •Pin group configuration

## 2.2.2.7 Shared Peripheral Bus Arbiter (SPBA)

The SPBA provides an arbitration mechanism to allow multiple masters to have access to the shared peripherals. The SPBA implementation under MSL defines the API to allow different masters to take or release ownership of a shared peripheral. These functions are also exported so that they can be used by other loadable modules.

## 2.3 Drivers

Many drivers are provided by Freescale that are specific to the peripherals on the i.MX family of processors or to the development platforms. Many of these drivers are common across all of the platforms. Most can be compiled into the kernel or compiled as object modules which can be dynamically loaded from a file system through insmod or modprobe. Modules can be loaded automatically as required using the kernel auto-load feature. The BSP contains a modules.dep file and a modprobe.conf file that contain the dependency information for the modules.

The i.MX multimedia applications processors have several classes of drivers, explained in the following sections.

## 2.3.1 Universal Asynchronous Receiver/Transmitter (UART) Driver

The i.MX family of processors support a Universal Asynchronous Receiver/Transmitter (UART) driver.

## 2.3.1.1 Debug Asynchronous Receiver/Transmitter (UART)

The Debug UART driver provides an interface to the i.MX28 Debug UART controller. It provides the standard Linux serial driver API. The following features are supported:

- •Interrupt driven transmit/receive of characters

- •Standard Linux baud rates up to 115 Kbps

- •Receive and transmit FIFOs support

- •Transmitting and receiving characters with 5, 6, 7 or 8-bit character lengths

- •Odd and even parity

- •CTS/RTS hardware flow control

- •Send and receive break characters through the standard Linux serial API

- •Recognize break and parity errors

- •Supports the standard TTY layer IOCTL calls

- •Console support required to bring up the command prompt through Debug serial port

- •Power management features by suspending and resuming UART ports

Currently, the Debug UART driver is used by default to bring up the console. DMA is not supported by this driver. The Debug UART can be accessed through the /dev/ttyAM0 device file.

#### 2.3.1.2 Application Asynchronous Receiver/Transmitter (UART)

The Application UART driver provides an interface to the i.MX28 Debug UART controller. It provides the standard Linux serial driver API. The following features are supported:

- •Interrupt and DMA driven transmit/receive of characters

- •Standard Linux baud rates up to 3 Mb/s

- •Transmitting and receiving characters with 5, 6, 7 or 8-bit character lengths

- •Odd and even parity

- •CTS/RTS hardware flow control

- •Send and receive break characters through the standard Linux serial API

- •Recognize break and parity errors

- •Supports the standard TTY layer IOCTL calls

- •Includes console support required to bring up the command prompt through the Debug serial port

- •Supports power management features by suspending and resuming UART ports

The application UART can be accessed through the /dev/ttySP0 device file.

#### 2.3.2 Real-Time Clock (RTC) Driver

The RTC is the clock that keeps the date and time while the system is running and even when the system is inactive. The RTC implementation supports IOCTL calls to read time, set time, set up periodic interrupts, and set up alarms. Linux defines the RTC API.

#### 2.3.3 Watchdog Timer (WDOG) Driver

The Watchdog timer protects against system failures by providing a method of escaping from unexpected events or programming errors.

The WDOG software implementation provides routines to service the WDOG timer, so that the timeout does not occur. The WDOG is serviced (at the same time for the platforms with two WDOGs) if it is already enabled before the Linux kernel boots (enabled by boot loader or ROM) with a configurable service interval. In addition, compile-time options specify whether the Linux kernel should enable the watchdog, and if so, which parameters should be used. If the second WDOG is present (used to generate an interrupt after the timeout occurs), the highest interrupt priority (number 16) is assigned to the WDOG interrupt.

The Linux OS has a standard WDOG interface that allows a WDOG driver for a specific platform to be supported. This is supported under all i.MX platforms.

#### 2.3.4 DCP

The DCP driver performs AES EBC decryption and encryption using the hardware OTP key that is not accessible from user space. The driver configures the i.MX28 DCP engine to AES 128-bit EBC mode and only supports encrypting/decrypting of a single 128-bit block.

The main purpose of this driver is to implement an interface to the DCP cryptography engine which is necessary for boot stream image verification performed before writing the boot stream to NAND flash. The driver implements a simple IOCTL interface to decrypt and encrypt a single 128-bit block.

#### 2.3.5 i.MX28 Graphics

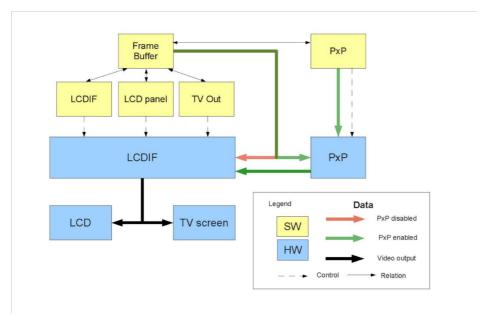

The graphics component consists of a number of Linux kernel drivers that implement the standard Linux kernel interface to the i.MX28 hardware to manipulate video buffers and output them to an LCD panel or TV screen. The graphic support includes the following components:

•Frame buffer driver

•LCDIF driver

•Pixel Pipeline (PxP) driver

•LCD panel driver

Figure 2-2 shows a block diagram of the i.MX28 Linux kernel graphic components and their relationship to each other.

Figure 2-2. **i.MX28** Kernel Graphic Components

## 2.3.5.1 LCDIF Driver

The i.MX28 LCDIF driver implements the Linux kernel-space API for basic LCD interface operations such as initialization, as well as LCD interface DMA abstraction for the callers. The interface is used by other graphics components such as the LCD panel drivers or the Frame buffer driver.

## 2.3.5.2 LCD Panel Drivers

LCD panel drivers provide an abstraction of a video output device for the Frame buffer driver. The LCD panel driver implements specific LCDIF initialization and exposes a set of API calls to the frame buffer driver so that it can control video output devices and perform dynamic switching between them (for example, run-time switching between the LCD panel and TV-output).

## 2.3.5.3 Frame Buffer Driver

The Frame buffer driver implements a standard Linux fbdev interface for user space applications and controls dynamic switching between different video outputs per user request.

## 2.3.5.4 Pixel Pipeline (PXP) Driver

The PxP driver implements a Video for Linux (V4L2) interface to the i.MX28 PxP hardware capable of performing various manipulations with video buffers such as scaling, cropping, rotation, alpha blending and so on. The PxP module handles a video stream received from user space from the V4L interface, then combines it with the frame buffer image and outputs the final image to the LCDIF module.

The graphics components can operate in two modes, with PxP enabled or disabled. Figure 2-2 shows the different video data flows depending on different modes.

#### 2.3.6 Sound Driver

The components of the audio subsystem are applications, the Advanced Linux Sound Architecture (ALSA), the audio driver, and the hardware. Applications interface with the ALSA, and the ALSA interfaces with the audio driver, which in turn controls the hardware of the audio subsystem. For more information about ALSA, see <u>www.alsa-project.org</u>.

The sound driver runs on the ARM processor. Digital audio data is carried over the digital audio link interface to the codec hardware. This is managed by the audio driver. There may be one or more audio streams, depending on the codec, such as voice or stereo DAC. The audio driver configures sample rates, formats, and audio clocks. The audio driver also manages the setup and control of the codec, DMA, and audio accessories, such as headphones and microphone detection. Stream mixing may also be supported, depending on the codec.

#### 2.3.7 Keypad

The keypad driver interfaces Linux to the keypad ladder connected to the i.MX28 LRADC controller. The software operation of the driver follows the Linux keyboard architecture. The driver is driven by interrupts generated by the LRADC controller when changing a signal on the keypad ladder input pin. The driver reads a current voltage on the LRADC pin, detects which key is being pressed and sends a key code to the upper layer. The driver detects long key presses and reports them as multiple key press events. The keypad driver may be used as a wake-up source for low-power standby mode.

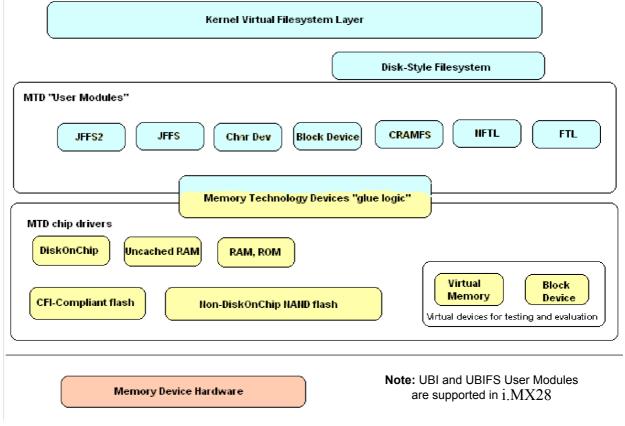

#### 2.3.8 Memory Technology Device (MTD) Driver

MTDs in Linux cover all memory devices, such as RAM, ROM, and different kinds of Flashes. As each memory device has its own idiosyncrasies in terms of read and write, the MTD subsystem provides a unified and uniform access to the various memory devices.

Figure 2-3 shows the MTD architecture.

Figure 2-3 is excerpted from *Building Embedded Linux Systems*, which describes the MTD subsystem. The user modules should not be confused with kernel modules or any sort of user-land software abstraction. The term MTD user module refers to software modules within the kernel that enable access to the low-level MTD chip drivers by providing recognizable interfaces and abstractions to the higher levels of the kernel or, in some cases, to user space.

MTD chip drivers register with the MTD subsystem by providing a set of predefined callbacks and properties in the mtd\_info argument to the add\_mtd\_device() function. The callbacks an MTD driver has to provide are called by the MTD subsystem to carry out operations, such as erase, read, write, and sync.

#### 2.3.8.1 GPMI/NAND

The GPMI/NAND driver interfaces with the i.MX28 GPMI/NAND module that is able to interact with a variety of NAND flash chips with 2 Kbyte and 4 Kbyte page sizes. The driver implements a standard interface for the upper MTD subsystem layer and supports various file systems, such as JFFS2, UBIFS or different commodity file systems (for example, FAT or EXT2) created on top of the UBI FTL.

The GPMI/NAND driver supports the i.MX28 BCH HW Error Correcting Code (ECC) engine that speeds up NAND flash read and write operations

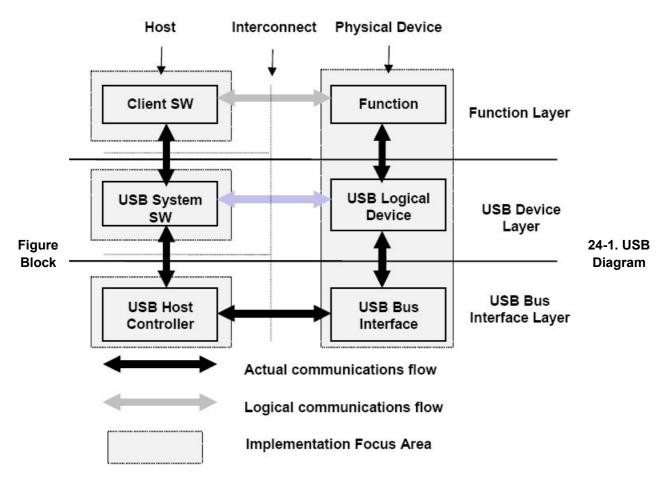

#### 2.3.9 USB Driver

The Linux kernel supports two main types of USB drivers: drivers on a host system and drivers on a device. A common USB host is a desktop computer. The USB drivers for a host system control the USB devices that are plugged into it. The USB drivers in a device, control how that single device looks to the host computer as a USB device. Because the term "USB device drivers" is very confusing, the USB developers have created the term "USB gadget drivers" to describe the drivers that control a USB device that connects to a computer.

#### 2.3.9.1USB Host-Side API Model

Within the Linux kernel, host-side drivers for USB devices talk to the usbcore APIs. The two types of public usbcore APIs, targeted at two different layers of USB driver:

- •General purpose drivers, exposed through driver frameworks such as block, character, or network devices.

- •Drivers that are part of the core, which are involved in managing a USB bus.

Such core drivers include the hub driver, which manages trees of USB devices, and several different kinds of Host Controller Drivers (HCDs), which control individual buses. See Chapter 2 of <u>http://www.kernel.org/doc/htmldocs/usb.html</u>, for more information.

The device model seen by USB drivers is relatively complex:

- •USB supports four kinds of data transfer (control, bulk, interrupt, and isochronous). Two transfer types use bandwidth as it is available (control and bulk), while the other two types of transfer (interrupt and isochronous) are scheduled to provide guaranteed bandwidth.

- •The device description model includes one or more configurations per device, only one of which is active at a time. Devices that are capable of high speed operation must also support full speed configurations, along with a way to ask about the other speed configurations that might be used.

- •Configurations have one or more interfaces. Interfaces may be standardized by USB Class specifications, or may be specific to a vendor or device.

- •Interfaces have one or more endpoints, each of which supports one type and direction of data transfer such as bulk out or interrupt in.

- •The only host-side drivers that actually touch hardware (reading/writing registers, handling IRQs, and so on) are the HCDs.

#### 2.3.9.2USB Device-Side Gadget Framework

The Linux Gadget API can be used by peripherals, which act in the USB device (slave) role.

Components of the Gadget Framework (see <u>http://www.linux-usb.org/gadget/</u>) are as follows :

- •Peripheral Controller Drivers—implement the Gadget API, and are the only layers that talk directly to the hardware. Different controller hardware needs different drivers, which may also need board-specific customization. These provide a software gadget device, visible in sysfs. This device can be thought of as being the virtual hardware to which the higher-level drivers are written.

- •Gadget Drivers—use the Gadget API, and can often be written to be hardware-neutral. A gadget driver implements one or more functions, each providing a different capability to the USB host, such as a network link or speakers.

- •Upper Layers, such as the network, file system, or block I/O subsystems—generate and consume the data that the gadget driver transfers to the host through the controller driver.

#### 2.3.9.3USB OTG Framework

Systems need specialized hardware support to implement OTG, including a special Mini-AB jack and associated transceiver to support Dual-Role operation. They can act either as a host, using the standard Linux-USB host side driver stack, or as a peripheral, using the Gadget framework. To do that, the system software relies on small additions to those programming interfaces, and on a new internal component (here called an OTG Controller) affecting which driver stack connects to the OTG port. In each role, the system can re-use the existing pool of hardware-neutral drivers, layered on top of the controller driver interfaces (usb\_bus or usb\_gadget). Such drivers need at most minor changes, and most of the calls added to support OTG can also benefit non-OTG products.

- •Gadget drivers test the is\_otg flag, and use it to determine whether or not to include an OTG descriptor in each of their configurations.

- •Gadget drivers may need changes to support the two new OTG protocols, exposed in new gadget attributes such as b\_hnp\_enable flag. HNP support should be reported through a user interface

(two LEDs could suffice), and is triggered in some cases when the host suspends the peripheral. SRP support can be user-initiated just like remote wakeup, probably by pressing the same button.

- •On the host side, USB device drivers need to be taught to trigger HNP at appropriate moments, using usb\_suspend\_device(). That also conserves battery power, which is useful even for non-OTG configurations.

- •Also on the host side, a driver must support the OTG Targeted Peripheral List, a whitelist used to reject peripherals not supported with a given Linux OTG host. This whitelist is product-specific—each product must modify otg\_whitelist.h to match its interoperability specification.

Non-OTG Linux hosts, such as PCs and workstations, normally have some solution for adding drivers, so that peripherals that are not recognized can eventually be supported. That approach is unreasonable for consumer products that may never have their firmware upgraded, and where it is usually unrealistic to expect traditional PC/workstation/server kinds of support model to work. For example, it is often impractical to change device firmware after the product has been distributed, so driver bugs cannot normally be fixed if they are found after shipment.

Additional changes are required below those hardware-neutral usb\_bus and usb\_gadget driver interfaces but those are not discussed here. Those affect the hardware-specific code for each USB Host or Peripheral controller, and how the HCD initializes (since OTG can be active only on a single port). They also involve what may be called an OTG Controller Driver, managing the OTG transceiver and the OTG state machine logic as well as much of the root hub behavior for the OTG port. The OTG controller driver needs to activate and deactivate USB controllers depending on the relevant device role. Some related changes were required inside usbcore, so that it can identify OTG-capable devices and respond appropriately to HNP or SRP protocols.

#### 2.3.10 General Drivers

General drivers discussed in the following sections, include the following:

- •Multimedia Card (MMC)/Secure Digital (SD) driver

- •I<sup>2</sup>C Client and Bus drivers