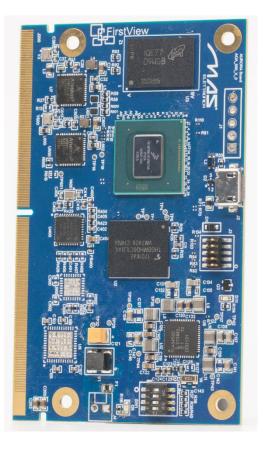

# **IMX8M Plus**

Hardware Manual

000

# **Revision History:**

| Doc. Version | IMX8MP SOM | Date       | Change                    |

|--------------|------------|------------|---------------------------|

|              | Version    |            |                           |

| V0.1         | REV1.0     | 2021-09-06 | Initial Version           |

| V1.0         | REV1.0     | 2023-04-26 | Updated Section 4.3       |

| V1.1         | REV1.1     | 2023-05-17 | Updated as per SOM Rev1.1 |

# Introduction

# 1.1 The SMARC Formfactor

The SMARC ("Smart Mobility ARChitecture") is a versatile small form factor computer on Module definition targeting applications that require low power, low costs, and high performance. The Modules will typically use ARM SOCs similar or the same as those used in many familiar devices such as tablet computers and smart phones. Alternative low power SOCs and CPUs, such as tablet oriented X86 devices and other RISC CPU's may be used as well. The Module power envelope is typically under 6W although designs up to about 15W are possible.

Two Module sizes are defined: 82 mm x 50 mm and 82 mm x 80 mm. The Module PCBs have 314 edge fingers that mate with a low profile 314 pin 0.5 mm

pitch right angle connector (the connector is sometimes identified as a 321-pin connector, but 7 pins are lost to the key).

The Modules are used as building blocks for portable and stationary embedded systems. The core CPU and support circuits, including DRAM, boot flash, power sequencing, CPU power supplies, GBE and dual channel LVDS display transmitter are concentrated on the Module. The Modules are used with application specific Carrier Boards that implement other features such as audio CODECs, touch controllers, wireless devices, etc. The modular approach allows scalability, fast time to market and upgradability while still maintaining low costs, low power and small physical size.

SMARC module and carrier specifications are available online at: https://www.sget.org/standards/smarc.html

# 2.0 Specifications

# 2.1 Core System

#### SOC:

NXP iMX8M Plus Series

- i.MX8M Plus Dual NXP i.MX8M Plus Dual, dual-core ARM Cortex-A53, 1.8GHz

- i.MX8M Plus Quad Lite NXP i.MX8M Plus Quad Lite, Quad-core ARM Cortex-A53, 1.8GHz

- i.MX8M Plus Quad: NXP i.MX8M Plus Quad, quad-core ARM Cortex-A53, 1.6GHz/1.8GHz

available either as industrial (-40°C to +105°C) or consumer (0°C to +95°C) type"

#### For more info about the processor NXP:

iMX8M Plus

L2 Cache

512 KB unified L2 cache

#### Memory

- 1GB 6GB, LPDDR4 up to 1.5Ghz

- Supports 32-bit LPDDR4-4000 and DDR4-3200

#### **IOT Security (Cybersecurity)**

OPTIGA<sup>™</sup> TPM SLB 9670 TPM2.0 Infineon Chip.

- Compliant to TPM Main Specification, Family "2.0"

- Random Number Generator (RNG) according to NIST SP800-90°

- Full personalization with Endorsement Key (EK) and EK certificate

- Support of cryptographic algorithms RSA-1028, RSA-2048, ECC NIST P256, ECC BN256, SHA-1, SHA-256

- JEDEC JESD47 industrial qualification

# 2.2 Video

IMX8M Plus standard display support consists of 1080P capable ePD, single/dual channel 24-bit LVDS and MIPI DSI. The LVDS output is derived from an DSI to LVDS, and the module can output 4-lane DSI.

#### **3D GPU Core:**

- Supports OpenGL ES 1.1, 2.0, 3.0,

- OpenCL 1.2, Vulkan

- Trust Zone support using a local MMU to manage secure regions

#### 2D GPU Core:

Multi-pipe 2D raster graphics core that accelerates the 2D graphics display.

#### LVDS

- LVDS Display Bridge (LDB) supports two channels; each channel has following signals:

- One clock pair and four data pairs.

- One LCDIF drives LVDS Tx, up to 1920x1080p60.

#### **MIPI DSI(Optional)**

- MIPI DSI are muxing with LVDS0 signals, in future, we can mount the DNP resistor at processor end.

- Supports one 4-lane MIPI DSI interface operating up to a maximum bit rate of 1.5 Gbps and maximum resolution of 1080p@60fps display output.

#### **Camera support**

- Compatible with the MIPI Alliance Interface specification v2.0

- Two MIPI-CSI camera inputs with 4-lane each.

# **2.3 Ethernet**

#### LAN

SOC embedded with two GbE ETH0 & ETH1 Controller with YT8511H Controller with IEEE-802.3 Supports 10/100/1000Mbps data transfer rates, both full-duplex /half-duplex".

One channel is connected directly to the SoC Ethernet signals, and the second channel is multiplexed with SAI interface.

# 2.4 Extension busses

## PCIe

1x PCI Express (PCIe)

- Single lane supporting PCIe Gen2

- Dual mode operation to function as root complex or endpoint.

- Integrated PHY interface

- Support L1 low power sub-state

#### USB

$4x\ USB\ 3.0\ /2.0$  and,  $1x\ USB\ 3.0\ OTG$

# UART

4x UART interface SER0 (Tx/Rx/CTS/RTS) and SER1(Tx/Rx), SER2(Tx/Rx/CTS/RTS), SER3 (Tx/Rx)

- High-speed TIA/EIA-232-F compatible.

- 7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none).

- Programmable baud rates up to 4 Mbps.

- 32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud.

- Serial IR interface low-speed, IrDA-compatible (up to 115.2 Kbit/s).

- Hardware flow control support for a request to send and clear to send signals.

- RS-485 driver direction control.

- DCE/DTE capability.

- RX\_DATA input and TX\_DATA output can be inverted respectively in RS-232/RS-485 mode.

- Various asynchronous wake mechanisms with the capability to wake the processor from STOP mode through an on-chip interruption.

#### CAN bus

2x CAN interfaces with the following features:

- Implements CAN V2.0B at 1 Mb/s: 0 to 8-byte length in the data field Standard and extended data and remote frames.

- Receive Buffers, Masks and Filters: Two receive buffers with prioritized message storage Six 29-bit filters Two 29-bit masks.

- Data Byte Filtering on the First Two Data Bytes (applies to standard data frames)

- Three Transmit Buffers with Prioritization and Abort Features.

- One-Shot mode Ensures Message Transmission is Attempted Only One Time.

- Clock Out Pin with Programmable Prescaler- Can be used as a clock source for other device(s)

- Start-of-Frame (SOF) Signal is Available for Monitoring the SOF Signal: Can be used for time slot-based protocols and/or bus diagnostics to detect early bus degradation.

- Interrupt Output Pin with Selectable Enables

- Buffer Full Output Pins Configurable as: Interrupt output for each receiver buffer General purpose output.

#### Page 8 of 56

## SPI

1 x SPI with the following features:

- Data rate up to 52 Mbit/s.

- Full-duplex synchronous serial interface.

- Master/Slave configurable.

- Up-to four chip-select signals to support multiple peripherals.

- Transfer continuation function allows unlimited length data transfers.

- 32-bit wide by 64-entry FIFO for both transmit and receive data.

- Polarity and phase of the Chip Select (SS) and SPI Clock (SCLK) are configurable.

- Direct Memory Access (DMA) support.

### **QSPI** Support

- Supports one Quad SPI serial flash devices, each with up to four bidirectional data lines. The key features include:

- Each channel can be configured as 1/2/4-bit operation.

- Support both dual-channel or single-channel operation

- Support both SDR mode and DDR mode

- External Memory Overview

- Support up to 166MHz SDR Mode and 166MHz DDR Mode (with external Flash device DQS input)

- Support up to 133MHz SDR Mode and 66MHz DDR Mode (with internal DQS

#### I2S

2x I2S interfaces with audio resolution from 16-bits to 32-bits and sample rate up to 384KHz.

The I2S (or I2S) module provides a synchronous audio interface (SAI) that supports full- duplex serial interfaces with frame synchronization such as I2S (see Audio Codec support)

### I2C

4x I2C interfaces

- Compliant with Philips I2C specification version 2.1

- Supports standard mode (up to 100K bits/s) and fast mode (up to 400K bits/s)

- Multi-master operation

- Master or Slave operation mode.

#### **GPIO**

12x GPIO 1.8V with interrupt.

# 2.5 System Storage

#### **SDIO**

1x SDIO (4-bit) compatible up to version 3.0.

The port is derived from the i.MX8M Plus on-chip MMC/SD/SDIO controller (uSDHC2). uSDHC IP supports the following main features:

- Fully compliant with MMC command/response sets and physical layer as defined in the multimedia card system specification, v5.1/v5.0/v4.4/v4.41/v4.4/v4.3/v4.2

- Fully compliant with SD command/response sets and physical layer as defined in the SD memory card specifications, v3.0 including high capacity SDXC cards up to 2 TB

- 1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to 25 MB/s

- 1-bit or 4-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes

- Dedicated card detection, write protection and Reset signals.

#### eMMC (8 Bit).

- Soldered on module 8, 16, 32, 64 or 128GB (build option) either standard or -40 to +85C temp range Compatible.

- MMC 5.1 compliance with HS400 DDR signaling to support up to 400 MB/sec.

- SD/SDIO 3.01 compliance with 200 MHz SDR signaling to support up to 100 MB/sec.

- Support for SDXC (extended capacity)

#### **EEPROM**

- Soldered on module 2Kbit memory (build option) either standard or -40 to +85C temp range Compatible.

- Interfaced with I2C4 bus. Supports 100KHz and 400KHz clock compatibility.

- Is using for storing the Unit Serial ID.

# 2.6 Boot Modes

Three Module pins allow the Carrier board user to select from eight possible boot devices. Three are Module devices, four are Carrier devices, and one is a remote device. Below the table from the Hardware specifications 2.0 of the boot modes:

|   | Carrier Connection |            | n          | Boot Source                                 |

|---|--------------------|------------|------------|---------------------------------------------|

|   | BOOT_SEL2#         | BOOT_SEL1# | BOOT_SEL0# | 1                                           |

| 0 | GND                | GND        | GND        | Carrier SATA                                |

| 1 | GND                | GND        | Float      | Carrier SD Card                             |

| 2 | GND                | Float      | GND        | Carrier eSPI (CS0#)                         |

| 3 | GND                | Float      | Float      | Carrier SPI (CS0#)                          |

| 4 | Float              | GND        | GND        | Module device (NAND, NOR) - vendor specific |

| 5 | Float              | GND        | Float      | Remote boot (GBE, serial) – vendor specific |

| 6 | Float              | Float      | GND        | Module eMMC Flash                           |

| 7 | Float              | Float      | Float      | Module SPI                                  |

Figure 1 BOOT SEL Selection

Below is the Boot selection table for the iMX8MPlus Processor, option provided on the SOM board for power ON the standalone SOM.

///

ELETTRON

| Boot selection table for the iMX8MP processor |   |   |   |   |

|-----------------------------------------------|---|---|---|---|

| BOOT_MODE                                     | 3 | 2 | 1 | 0 |

| BOOT FROM FUSE                                | 0 | 0 | 0 | 0 |

| SERIAL DOWNLOAD                               | 0 | 0 | 0 | 1 |

| eMMC                                          |   | 0 | 1 | 0 |

| SD BOOT                                       | 0 | 0 | 1 | 1 |

# 2.7 Power

Supply Voltage

$4.75 \ V - 5.25 \ V$

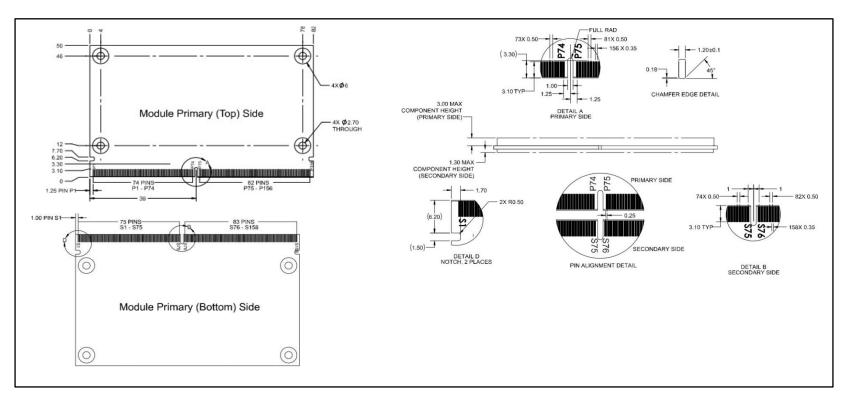

# 2.8 Mechanical and Environmental

#### **Form Factor**

SGET SMARC Specifications v2.0/2.1 (2.1 is currently under approval by SGET)

#### Dimension

SMARC small size module, 82mm x 50mm

#### **Operating Temperature**

Standard: 0°C to +60°C

Rugged: -20°C to +85°C (optional)

#### Humidity

5-90% RH operating, non-condensing5-95% RH storage (and operating with conformal coating)

#### **Shock and Vibration**

IEC 60068-2-64 and IEC-60068-2-27, MIL-STD-202 F, Method 213B, Table 213-I, Condition A and Method 214A, Table 214-I, Condition

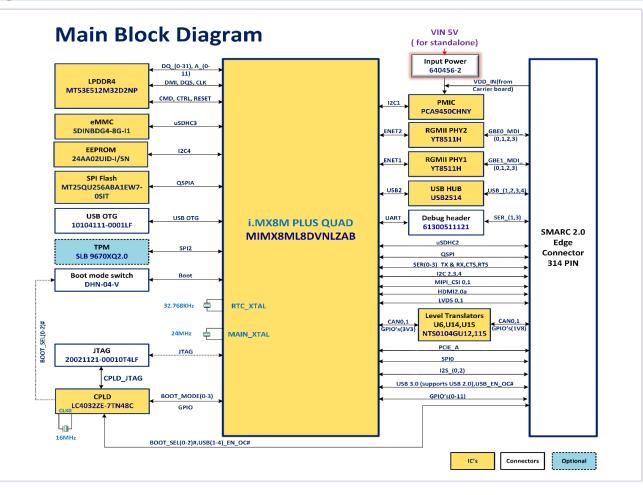

# 3. Block Diagram

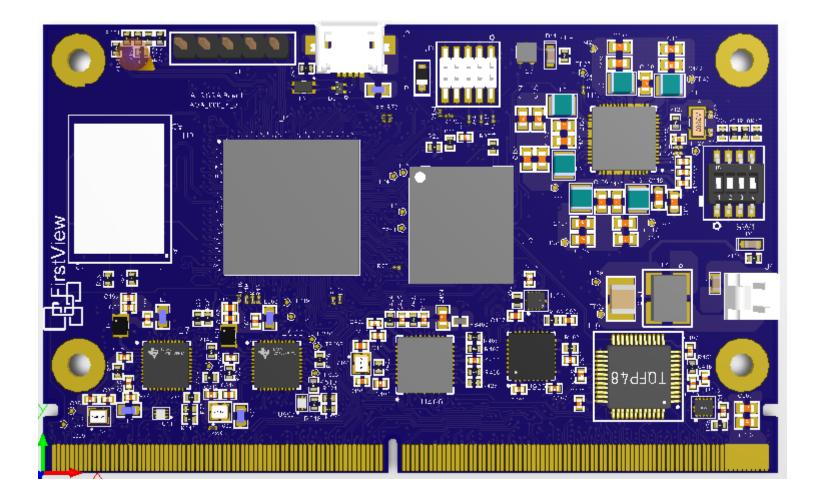

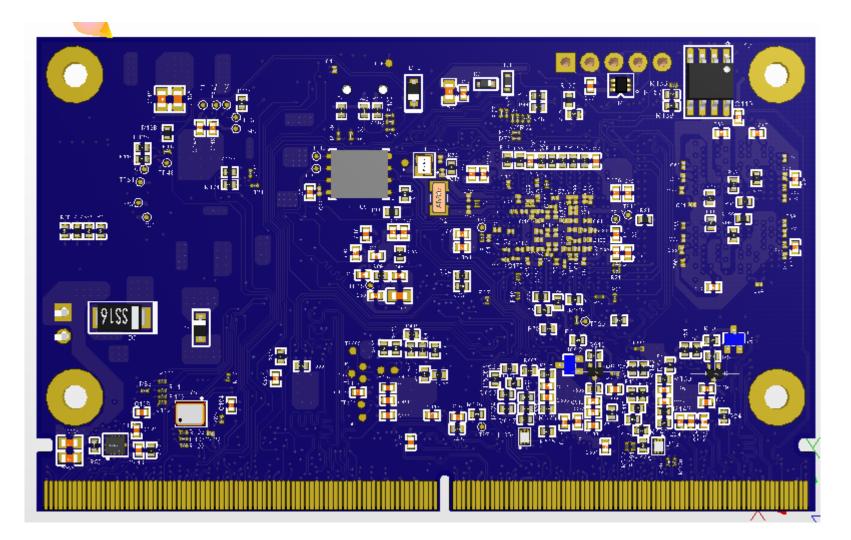

Figure 2 – Module function diagram

Page 15 of 56

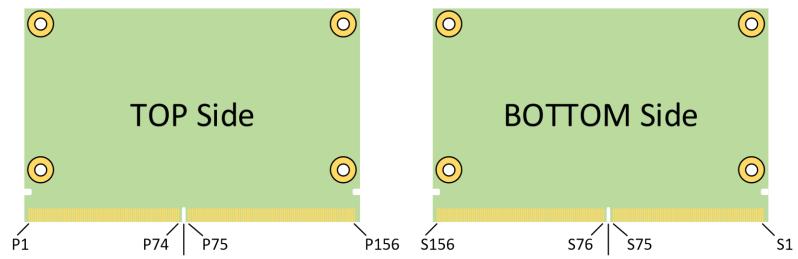

# 4.0. Pinout and Signal Descriptions

The IMX8M Plus SOM Module pins are designated as P1 – P156 on the Module Primary (Top) side, and S1 – S158 on the Module Secondary (Bottom) side. There is a total

of 314 pins on the Module. The connector is sometimes identified as a 321 pin connector, but 7 pins are lost to the key (4 on the primary side and 3 on secondary side).

The Secondary (Bottom) side faces the Carrier board when a normal or standard Carrier connector is used. Some connector vendors offer "reverse" pin-out connectors, which

effectively flip the Module over such that the Module Primary side would face the Carrier board.

The SMARC Module pins are deliberately numbered as P1 - P156 and S1 - S158 for clarity and to differentiate the SMARC Module from MXM3 graphics modules, which use the same connector but use the pins for very different functions. MXM3 cards and MXM3 baseboard connectors use a different pin numbering scheme.

The below table is a comprehensible list of all signal pins on the MXM 3 connector in the standard specification SMARC 2.1.

Those signals not supported on IMX8M Plus are strikethroughs.

Figure 3 Module top/bottom side pin numbering

Page 16 of 56

# 4.1. Module Pinout Top Side P

| P-Pin Primary (Top) Side |                |  |

|--------------------------|----------------|--|

| P1                       | SMB_ALERT_1V8# |  |

| P2                       | GND            |  |

| P3                       | CSI1_CK+       |  |

| P4                       | CSI1_CK        |  |

| P5                       | GBE1_SDP       |  |

| P6                       | GBE0_SDP       |  |

| P7                       | CSI1_RX0+      |  |

| P8                       | CSI1_RX0-      |  |

| P9                       | GND            |  |

| P10                      | CSI1_RX1+      |  |

| P11                      | CSI1_RX1-      |  |

| P12                      | GND            |  |

| P13                      | CSI1_RX2+      |  |

| P14                      | CSI1 RX2-      |  |

| P15                      | GND            |  |

| P16                      | CSI1 RX3+      |  |

| P17                      | CSI1 RX3-      |  |

| P18                      | GND            |  |

| P19                      | GBE0 MDI3-     |  |

| P-Pin Primary (Top) Side |                |  |

|--------------------------|----------------|--|

| P21                      | GBE0_LINK100#  |  |

| P22                      | GBE0_LINK1000# |  |

| P23                      | GBE0_MDI2-     |  |

| P24                      | GBE0_MDI2+     |  |

| P25                      | GBE0_LINK_ACT# |  |

| P26                      | GBE0_MDI1-     |  |

| P27                      | GBE0_MDI1+     |  |

| P28                      | GBE0_CTREF     |  |

| P29                      | GBE0_MDI0-     |  |

| P30                      | GBE0_MDI0+     |  |

| P31                      | SPI0_CS1#      |  |

| P32                      | GND            |  |

| P33                      | SDIO_WP        |  |

| P34                      | SDIO_CMD       |  |

| P35                      | SDIO_CD#       |  |

| P36                      | SDIO_CK        |  |

| P37                      | SDIO_PWR_EN    |  |

| P38                      | GND            |  |

| P39                      | SDIO_D0        |  |

| P-Pin Primary (Top)<br>Side |           |  |

|-----------------------------|-----------|--|

| P41                         | SDIO_D2   |  |

| P42                         | SDIO_D3   |  |

| P43                         | SPI0_CS0# |  |

| P44                         | SPI0_CK   |  |

| P45                         | SPI0_DIN  |  |

| P46                         | SPI0_DO   |  |

| P47                         | GND       |  |

| P48                         | SATA_TX+  |  |

| P49                         | SATA_TX   |  |

| P50                         | GND       |  |

| P51                         | SATA_RX+  |  |

| P52                         | SATA_RX   |  |

| P53                         | GND       |  |

| P54                         | ESPI_CS0# |  |

| P55                         | ESPI_CS1# |  |

| P56                         | ESPI_CK   |  |

| P57                         | ESPI_IO_0 |  |

| P58                         | ESPI_IO_1 |  |

| P59                         | GND       |  |

| P-Pi | P-Pin Primary (Top) Side |  |

|------|--------------------------|--|

| P61  | USB0-                    |  |

| P62  | USB0_EN_OC#              |  |

| P63  | USB0_VBUS_DET            |  |

| P64  | USB0_OTG_ID              |  |

| P65  | USB1+                    |  |

| P66  | USB1-                    |  |

| P67  | USB1_EN_OC#              |  |

| P68  | GND                      |  |

| P69  | USB2+                    |  |

| P70  | USB2-                    |  |

| P71  | USB2_EN_OC#              |  |

| P72  | RSVD                     |  |

| P73  | RSVD                     |  |

| P74  | USB3_EN_OC#              |  |

|      | Key                      |  |

| P75  | PCIE_A_RST#              |  |

| P76  | USB4_EN_OC#              |  |

| P77  | RSVD                     |  |

| P78  | RSVD                     |  |

| P-Pin Primary (Top) Side |                          |  |

|--------------------------|--------------------------|--|

| P80                      | PCIE_C_REFCK+            |  |

| P81                      | PCIE_C_REFCK             |  |

| P82                      | GND                      |  |

| P83                      | PCIE_A_REFCK+            |  |

| P84                      | PCIE_A_REFCK             |  |

| P85                      | GND                      |  |

| P86                      | PCIE_A_RX+               |  |

| P87                      | PCIE A RX-               |  |

| P88                      | GND                      |  |

| P89                      | PCIE_A_TX+               |  |

| P90                      | PCIE_A_TX-               |  |

| P91                      | GND                      |  |

| P92                      | HDMI_D2+ /<br>DP1_LANE0+ |  |

| P93                      | HDMI_D2-/                |  |

| <b>D</b> O (             | DP1_LANE0-               |  |

| P94                      | GND                      |  |

| P95                      | HDMI_D1+ /               |  |

| DOC                      | DP1_LANE1+               |  |

| P96                      | HDMI_D1- /<br>DP1 LANE1- |  |

| P97                      | GND                      |  |

| P98                      | HDMI_D0+ /<br>DP1_LANE2+ |  |

P20 GBE0 MDI3+

P40 SDIO D1

P60 USB0+

P79 GND

P99 HDMI\_D0- / DP1\_LANE2-

| P-Pin Primary (Top) Side |                          |  |

|--------------------------|--------------------------|--|

| P100                     | GND                      |  |

| P101                     | HDMI_CK+ / DP1_LANE3+    |  |

| P102                     | HDMI_CK- / DP1_LANE3-    |  |

| P103                     | GND                      |  |

| P104                     | HDMI_HPD / DP1_HPD       |  |

| P105                     | HDMI_CTRL_CK / DP1_AUX+  |  |

| P106                     | HDMI_CTRL_DAT / DP1_AUX- |  |

| P107                     | DP1_AUX_SEL              |  |

| P108                     | GPIO0 / CAM0_PWR#        |  |

| P109                     | GPIO1 / CAM1_PWR#        |  |

| P110                     | GPIO2 / CAM0_RST#        |  |

| P111                     | GPIO3 / CAM1_RST#        |  |

|                          |                          |  |

|                          |                          |  |

|                          |                          |  |

|                          |                          |  |

| P-Pin Primary (Top) Side |                  |  |

|--------------------------|------------------|--|

| P112                     | GPIO4 / HDA_RST# |  |

| P113                     | GPIO5 / PWM_OUT  |  |

| P114                     | GPIO6 / TACHIN   |  |

| P115                     | GPIO7            |  |

| P116                     | GPIO8            |  |

| P117                     | GPIO9            |  |

| P118                     | GPIO10           |  |

| P119                     | GPIO11           |  |

| P120                     | GND              |  |

| P121                     | I2C_PM_CK        |  |

| P122                     | I2C_PM_DAT       |  |

| P123                     | BOOT_SEL0#       |  |

| P124                     | BOOT_SEL1#       |  |

| P125                     | BOOT_SEL2#       |  |

| P126                     | RESET_OUT#       |  |

|                          |                  |  |

| P-Pin | Primary (Top) Side |

|-------|--------------------|

| P127  | RESET_IN#          |

| P128  | POWER_BTN#         |

| P129  | SER0_TX            |

| P130  | SER0_RX            |

| P131  | SER0_RTS#          |

| P132  | SER0_CTS#          |

| P133  | GND                |

| P134  | SER1_TX            |

| P135  | SER1_RX            |

| P136  | SER2_TX            |

| P137  | SER2_RX            |

| P138  | SER2_RTS#          |

| P139  | SER2_CTS#          |

| P140  | SER3_TX            |

| P141  | SER3_RX            |

|       |                    |

|       |                    |

| P-Pin Primary (Top) Side |         |  |

|--------------------------|---------|--|

| P142                     | GND     |  |

| P143                     | CAN0_TX |  |

| P144                     | CAN0_RX |  |

| P145                     | CAN1_TX |  |

| P146                     | CAN1_RX |  |

| P147                     | VDD_IN  |  |

| P148                     | VDD_IN  |  |

| P149                     | VDD_IN  |  |

| P150                     | VDD_IN  |  |

| P151                     | VDD_IN  |  |

| P152                     | VDD_IN  |  |

| P153                     | VDD_IN  |  |

| P154                     | VDD_IN  |  |

| P155                     | VDD_IN  |  |

| P156                     | VDD_IN  |  |

|                          |         |  |

# 4.2. Module Pinout Bottom Side S

| SI  | Pin Secondary (Bott) Side |

|-----|---------------------------|

| S1  | CSI1_TX+/I2C_CAM1_CK      |

| S2  | CSI1_TX-/I2C_CAM1_DAT     |

| S3  | GND                       |

| S4  | RSVD                      |

| S5  | CSI0_TX-/I2C_CAM0_CK      |

| S6  | CAM_MCK                   |

| S7  | CSI0_TX+/I2C_CAM0_DAT     |

| S8  | CSI0_CK+                  |

| S9  | CSI0_CK-                  |

| S10 | GND                       |

| S11 | CSI0_RX0+                 |

| S12 | CSI0_RX0-                 |

| S13 | GND                       |

| S14 | CSI0_RX1+                 |

| S15 | CSI0_RX1-                 |

| S16 | GND                       |

| S17 | GBE1_MDI0+                |

| S18 | GBE1_MDI0-                |

| S19 | GBE1_LINK100#             |

| S20 | GBE1_MDI1+                |

| SPin Secondary |                |  |  |  |

|----------------|----------------|--|--|--|

|                | (Bott) Side    |  |  |  |

| S21            | GBE1_MDI1-     |  |  |  |

| S22            | GBE1_LINK1000# |  |  |  |

| S23            | GBE1_MDI2+     |  |  |  |

| S24            | GBE1_MDI2-     |  |  |  |

| S25            | GND            |  |  |  |

| S26            | GBE1_MDI3+     |  |  |  |

| S27            | GBE1_MDI3-     |  |  |  |

| S28            | GBE1_CTREF     |  |  |  |

| S29            | PCIE_D_TX+     |  |  |  |

| S30            | PCIE_D_TX-     |  |  |  |

| S31            | GBE1_LINK_ACT# |  |  |  |

| S32            | PCIE_D_RX+     |  |  |  |

| S33            | PCIE_D_RX-     |  |  |  |

| S34            | GND            |  |  |  |

| S35            | USB4+          |  |  |  |

| S36            | USB4-          |  |  |  |

| S37            | USB3_VBUS_DET  |  |  |  |

| S38            | AUDIO_MCK      |  |  |  |

| S39            | I2S0_LRCK      |  |  |  |

| S40            | I2S0_SDOUT     |  |  |  |

| SPi | n Secondary (Bott) Side |

|-----|-------------------------|

| S41 | I2S0_SDIN               |

| S42 | I2S0_CK                 |

| S43 | ESPI_ALERT0#            |

| S44 | ESPI_ALERT1#            |

| S45 | RSVD                    |

| S46 | RSVD                    |

| S47 | GND                     |

| S48 | I2C_GP_CK               |

| S49 | I2C_GP_DAT              |

| S50 | HDA_SYNC / I2S2_LRCK    |

| S51 | HDA_SDO / I2S2_SDOUT    |

| S52 | HDA_SDI / I2S2_SDIN     |

| S53 | HDA_CK / I2S2_CK        |

| S54 | SATA_ACT#               |

| S55 | USB5_EN_OC#             |

| S56 | ESPI_IO_2               |

| S57 | ESPI_IO_3               |

| S58 | ESPI_RESET#             |

| S59 | <del>USB5+</del>        |

| S60 | <del>USB5-</del>        |

| SPin Secondary |             |  |  |  |  |

|----------------|-------------|--|--|--|--|

| (Bott) Side    |             |  |  |  |  |

| S61            | GND         |  |  |  |  |

| S62            | USB3_SSTX+  |  |  |  |  |

| S63            | USB3_SSTX-  |  |  |  |  |

| S64            | GND         |  |  |  |  |

| S65            | USB3_SSRX+  |  |  |  |  |

| S66            | USB3_SSRX-  |  |  |  |  |

| S67            | GND         |  |  |  |  |

| S68            | USB3+       |  |  |  |  |

| S69            | USB3-       |  |  |  |  |

| S70            | GND         |  |  |  |  |

| S71            | USB2_SSTX+  |  |  |  |  |

| S72            | USB2_SSTX-  |  |  |  |  |

| S73            | GND         |  |  |  |  |

| S74            | USB2_SSRX+  |  |  |  |  |

| S75            | USB2_SSRX-  |  |  |  |  |

|                | KEY         |  |  |  |  |

| S76            | PCIE_B_RST# |  |  |  |  |

| S77            | PCIE_C_RST# |  |  |  |  |

| S78            | PCIE_C_RX+  |  |  |  |  |

| S79            | PCIE_C_RX-  |  |  |  |  |

| SPin Secondary (Bott)<br>Side |               |  |  |  |

|-------------------------------|---------------|--|--|--|

| S80                           | GND           |  |  |  |

| S81                           | PCIE_C_TX+    |  |  |  |

| S82                           | PCIE_C_TX-    |  |  |  |

| S83                           | GND           |  |  |  |

| S84                           | PCIE_B_REFCK+ |  |  |  |

| S85                           | PCIE_B_REFCK- |  |  |  |

| S86                           | GND           |  |  |  |

| S87                           | PCIE_B_RX+    |  |  |  |

| S88                           | PCIE_B_RX-    |  |  |  |

| S89                           | GND           |  |  |  |

| S90                           | PCIE_B_TX+    |  |  |  |

| S91                           | PCIE_B_TX-    |  |  |  |

| S92                           | GND           |  |  |  |

| S93                           | DP0_LANE0+    |  |  |  |

| S94                           | DP0_LANE0-    |  |  |  |

| S95                           | DP0_AUX_SEL   |  |  |  |

| S96                           | DP0_LANE1+    |  |  |  |

| S97                           | DP0_LANE1-    |  |  |  |

| S98                           | DP0_HPD       |  |  |  |

| S99                           | DP0_LANE2+    |  |  |  |

|      | SPin Secondary (Bott) Side        |

|------|-----------------------------------|

| S100 | DP0_LANE2-                        |

| S101 | GND                               |

| S102 | DP0_LANE3+                        |

| S103 | DP0_LANE3-                        |

| S104 | USB3_OTG_ID                       |

| S105 | DP0_AUX+                          |

| S106 | DP0_AUX-                          |

| S107 | LCD1_BKLT_EN                      |

| S108 | LVDS1_CK+ / eDP1_AUX+ / DSI1_CLK+ |

| S109 | LVDS1_CK-/eDP1_AUX-/DSI1_CLK-     |

| S110 | GND                               |

| S111 | LVDS1_0+ / eDP1_TX0+ / DSI1_D0+   |

| S112 | LVDS1_0- / eDP1_TX0- / DSI1_D0-   |

| S113 | eDP1_HPD                          |

| S114 | LVDS1_1+/eDP1_TX1+/DSI1_D1+       |

|      | SPin Secondary (Bott) Side      |

|------|---------------------------------|

| S115 | LVDS1_1-/eDP1_TX1-/DSI1_D1-     |

| S116 | LCD1_VDD_EN                     |

| S117 | LVDS1_2+ / eDP1_TX2+ / DSI1_D2+ |

| S118 | LVDS1_2- / eDP1_TX2- / DSI1_D2- |

| S119 | GND                             |

| S120 | LVDS1_3+ / eDP1_TX3+ / DSI1_D3+ |

| S121 | LVDS1_3- / eDP1_TX3- / DSI1_D3- |

| S122 | LCD1_BKLT_PWM                   |

| S123 | RSVD                            |

| S124 | GND                             |

| S125 | LVDS0_0+ / eDP0_TX0+ / DSI0_D0+ |

| S126 | LVDS0_0-/eDP0_TX0-/DSI0_D0-     |

| S127 | LCD0_BKLT_EN                    |

| S128 | LVDS0_1+ / eDP0_TX1+ / DSI0_D1+ |

| S129 | LVDS0_1-/eDP0_TX1-/DSI0_D1-     |

|      | SPin Secondary (Bott) Side        |

|------|-----------------------------------|

| S130 | GND                               |

| S131 | LVDS0_2+ / eDP0_TX2+ / DSI0_D2+   |

| S132 | LVDS0_2-/eDP0_TX2-/DSI0_D2-       |

| S133 | LCD0_VDD_EN                       |

| S134 | LVDS0_CK+ / eDP0_AUX+ / DSI0_CLK+ |

| S135 | LVDS0_CK- / eDP0_AUX- / DSI0_CLK- |

| S136 | GND                               |

| S137 | LVDS0_3+ / eDP0_TX3+ / DSI0_D3+   |

| S138 | LVDS0_3-/eDP0_TX3-/DSI0_D3-       |

| S139 | I2C_LCD_CK                        |

| S140 | I2C_LCD_DAT                       |

| S141 | LCD0_BKLT_PWM                     |

| S142 | RSVD                              |

| S143 | GND                               |

| S144 | eDP0_HPD                          |

| SP   | SPin Secondary (Bott)<br>Side |  |  |  |  |

|------|-------------------------------|--|--|--|--|

| S145 | WDT_TIME_OUT#                 |  |  |  |  |

| S146 | PCIE_WAKE#                    |  |  |  |  |

| S147 | VDD_RTC                       |  |  |  |  |

| S148 | LID#                          |  |  |  |  |

| S149 | SLEEP#                        |  |  |  |  |

| S150 | VIN_PWR_BAD#                  |  |  |  |  |

| S151 | CHARGING#                     |  |  |  |  |

| S152 | CHARGER_PRSNT#                |  |  |  |  |

| S153 | CARRIER_STBY#                 |  |  |  |  |

| S154 | CARRIER_PWR_ON                |  |  |  |  |

| S155 | FORCE_RECOV#                  |  |  |  |  |

| S156 | BATLOW#                       |  |  |  |  |

| S157 | TEST#                         |  |  |  |  |

| S158 | GND                           |  |  |  |  |

|      |                               |  |  |  |  |

# 4.3 Signal Terminology Descriptions

Meaning of the terms used for signal description tables

| Term        | Description                                                                                                       |

|-------------|-------------------------------------------------------------------------------------------------------------------|

| Ι           | Input to the module                                                                                               |

| 0           | Output from the module                                                                                            |

| O OD        | Open drain output from the module                                                                                 |

| I OD        | Open drain input to the module, with mandatory PU (pull up) on module                                             |

| OD          | Open drain                                                                                                        |

| I/O         | Bi-directional Input/Output                                                                                       |

| PU          | PU (pull-up) resistor on module                                                                                   |

| PD          | PD (pull-down) resistor on module                                                                                 |

| VDD_IN      | Main power source from carrier to module                                                                          |

| CMOS        | Logic input or output                                                                                             |

| GBE MDI     | Differential analog signaling for Gigabit Media Dependent Interface                                               |

| LVDS DP     | Low Voltage Differential Signal for DisplayPort interface                                                         |

| LVDS D-PHY  | Low Voltage Differential Signal for MIPI CSI-2 cameras and DSI displays                                           |

| LVDS M-PHY  | Low Voltage Differential Signal for MIPI CSI-3 cameras                                                            |

| LVDS LCD    | Low Voltage Differential Signal for LCD displays                                                                  |

| LVDS PCIE   | Low Voltage Differential Signal for PCIe                                                                          |

| USB         | DC coupled differential signaling for traditional (non-Superspeed) USB signals                                    |

| USB SS      | Differential signal for SuperSpeed USB signals                                                                    |

| USB VBUS 5V | 5V tolerant input for USB VBUS detection                                                                          |

| 3.3V        | 3.3V Power Domain: Active while CARRIER_PWRON is high and CARRIER_SBY# is NOT active (i.e. both signals are high) |

| 1.8V        | 1.8V Power Domain: Active while CARRIER_PWRON is high and CARRIER_SBY# is NOT active (i.e. both signals are high) |

| 3.3Vsb      | 3.3V Power Domain: Active while CARRIER_PWRON is high (regardless of CARRIER_SBY#)                                |

| 1.8Vsb      | 1.8V Power Domain: Active while CARRIER_PWRON is high (regardless of CARRIER_SBY#)                                |

# 4.3.1 LVDS0/LVDS1 MODE

IMX8M Plus has integrated the Dual channel LVDS0 & LVDS1. The following table shows the pins of the SMARC connector are used when the LVDS feature is enabled.

| Ball #                                               | Name                                                                                         | Pin #                                                                | Description                                                                     | I/O Туре      | I/O<br>Level | Power<br>Domain | PU /<br>PD | Comments |

|------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------|--------------|-----------------|------------|----------|

| D29<br>E28<br>E29<br>F28<br>G29<br>H28<br>H29<br>J28 | LVDS0_0+<br>LVDS0_0-<br>LVDS0_1+<br>LVDS0_1-<br>LVDS0_2+<br>LVDS0_2-<br>LVDS0_3+<br>LVDS0_3- | \$125<br>\$126<br>\$128<br>\$129<br>\$131<br>\$132<br>\$137<br>\$138 | Primary LVDS channel differential pair data lines                               | O LVDS LCD    |              | Runtime         |            |          |

| F29<br>G28                                           | LVDS0_CK+<br>LVDS0_CK-                                                                       | S134<br>S135                                                         | Primary LVDS channel differential pair clock lines                              | O LVDS<br>LCD |              | Runtime         |            |          |

| W25                                                  | LCD0_VDD_EN                                                                                  | S133                                                                 | Primary LVDS channel power enable, active high                                  | O<br>CMOS     | 1.8V         | Runtime         |            |          |

| Y29                                                  | LCD0_BKLT_EN                                                                                 | S127                                                                 | Primary LVDS channel backlight enable, active high                              | O<br>CMOS     | 1.8V         | Runtime         |            |          |

| AE18                                                 | LCD0_BKLT_PWM                                                                                | S141                                                                 | Primary LVDS channel brightness control through<br>pulse width modulation (PWM) | O<br>CMOS     | 1.8V         | Runtime         |            |          |

| Ball #                                               | Name                                                                                         | Pin #                                                 | Description                                                             | I/О Туре       | I/O<br>Level | Power<br>Domain | PU / PD | Comments |

|------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------|----------------|--------------|-----------------|---------|----------|

| A26<br>B26<br>A27<br>B27<br>B29<br>C28<br>C29<br>D28 | LVDS1_0+<br>LVDS1_0-<br>LVDS1_1+<br>LVDS1_1-<br>LVDS1_2+<br>LVDS1_2-<br>LVDS1_3+<br>LVDS1_3- | S111   S112   S114   S115   S117   S118   S120   S121 | Secondary LVDS channel differential pair data<br>lines                  | O LVDS<br>LCD  |              | Runtime         |         |          |

| A28<br>B28                                           | LVDS1_CK+<br>LVDS1_CK-                                                                       | S108<br>S109                                          | Secondary LVDS channel differential pair clock lines.                   | O LVDS<br>LCD  |              | Runtime         |         |          |

| W26                                                  | LCD1_VDD_EN                                                                                  | S116                                                  | Secondary panel power enable, active high                               | O<br>CMOS      | 1.8V         | Runtime         |         |          |

| Y28                                                  | LCD1_BKLT_EN                                                                                 | S107                                                  | Secondary panel backlight enable, active high                           | O<br>CMOS      | 1.8V         | Runtime         |         |          |

| AC18                                                 | LCD1_BKLT_PWM                                                                                | S122                                                  | Secondary panel brightness control through pulse width modulation (PWM) | O<br>CMOS      | 1.8V         | Runtime         |         |          |

| AJ6                                                  | I2C_LCD_DAT                                                                                  | S140                                                  | DDC data line used for flat panel detection and control                 | I/O OD<br>CMOS | 1.8V         | Runtime         | PU 2k2  |          |

| AJ7                                                  | I2C_LCD_CK                                                                                   | S139                                                  | DDC clock line used for flat panel detection and control                | O OD<br>CMOS   | 1.8V         | Runtime         | PU 2k2  |          |

# 4.3.2 MIPI CSI1 (Camera)

IMX8M Plus has integrated a MIPI-CSI interface with up-to four data lanes and one clock lanes with MIPI D-PHY specification V1.2 The

following table shows the pins of the SMARC connector are used when the MIPI CSI feature is enabled.

| Ball #                                               | Name                                                                                                 | Pin #                                              | Description                                                                      | І/О Туре                        | I/O<br>Level | Power<br>Domain | PU / PD | Comments                                                                  |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|--------------|-----------------|---------|---------------------------------------------------------------------------|

| D18<br>E18<br>D20<br>E20<br>D24<br>E24<br>D26<br>E26 | CSI1_RX0+<br>CSI1_RX0-<br>CSI1_RX1+<br>CSI1_RX1-<br>CSI1_RX2+<br>CSI1_RX2-<br>CSI1_RX3+<br>CSI1_RX3- | P7<br>P8<br>P10<br>P11<br>P13<br>P14<br>P16<br>P17 | CSI1 differential input<br>(point to point)                                      | I LVDS D-PHY<br>/ I LVDS M-PHY  |              | Runtime         |         |                                                                           |

| D22<br>E22                                           | CSI1_CK+<br>CSI1_CK-                                                                                 | P3<br>P4                                           | CSI1 differential clock<br>input (point to point)                                | I LVDS D-PHY                    |              | Runtime         |         |                                                                           |

| AE8                                                  | I2C_CAM1_DAT /<br>- <del>CSI1_TX-</del>                                                              | S2                                                 | I2C data for serial camera<br>data support link or<br>differential<br>data lane  | I/O OD CMOS<br>/ O LVDS MPHY    | 1.8V         | Runtime         | PU 2.2K | MIPI-CSI 2.0 mode uses<br>I2C_CAM1_DAT MIPI-CSI 3.0<br>mode uses CSI1_TX- |

| AH6                                                  | I2C_CAM1_CK /<br>- <del>CSI1_TX+</del>                                                               | S1                                                 | I2C clock for serial<br>camera data support<br>link or<br>differential data lane | O OD CMOS<br>/ O LVDS M-<br>PHY | 1.8V         | Runtime         | PU 2.2K | MIPI-CSI 2.0 mode uses<br>I2C_CAM1_CK MIPI-CSI 3.0<br>mode uses CSI1_TX+  |

| AA29                                                 | CAM1_PWR# /<br>GPIO1                                                                                 | P109                                               | Camera 0 Power Enable, active low output.                                        | O CMOS                          | 1.8V         | Runtime         |         | CAM1_PWR# is default, GPIO1<br>can be enabled through DVT                 |

| A7                                                   | CAM1_RST#/<br>GPIO3                                                                                  | P111                                               | Camera 0 reset, active low output                                                | O CMOS                          | 1.8V         | Runtime         |         | CAM1_PWR# is default, GPIO3<br>can be enabled through DVT                 |

| K29                                                  | CAM_MCK                                                                                              | S6                                                 | Master clock output                                                              | O CMOS                          | 1.8V         | Runtime         |         | This signal is used by both CSI0 and CSI1                                 |

| A25<br>B25<br>A24<br>B24               | CSI0_RX0+<br>CSI0_RX0-<br>CSI0_RX1+<br>CSI0_RX1-                     | \$11<br>\$12<br>\$14<br>\$15               | CSI0 differential input<br>(point to point)       | I LVDS D-PHY<br>/ I LVDS M-PHY | Runtime |                                                                               |                |

|----------------------------------------|----------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------|--------------------------------|---------|-------------------------------------------------------------------------------|----------------|

| A23<br>B23<br>A22<br>B22<br>A21<br>B21 | CSI0_CK+<br>CSI0_CK-<br>CSI0_D2+<br>CSI0_D2-<br>CSI0_D3+<br>CSI0_D3- | \$8<br>\$9<br>\$32<br>\$33<br>\$29<br>\$30 | CSI0 differential clock<br>input (point to point) | I LVDS D-PHY                   | Runtime | CSI0_D2+<br>CSI0_D2-<br>CSI0_D3+<br>CSI0_D3-<br>Signals are connected<br>pin, | to PCIe TX, RX |

# 4.3.3 I2S (Audio)

IMX8M Plus has integrated a I2S interface The I2S (or I2S) module provides a synchronous audio interface (SAI) that supports, full-duplex serial interfaces with frame synchronization.

The following table shows the pins of the SMARC connector that are used when the I2S feature is enabled.

| Ball# | Name       | Pin # | Description                                | I/О<br>Туре | I/O<br>Level | Power<br>Domain | PU / PD | Comments                                                                              |

|-------|------------|-------|--------------------------------------------|-------------|--------------|-----------------|---------|---------------------------------------------------------------------------------------|

| AC16  | I2S0_LRCK  | S39   | I2S0 Left & Right<br>synchronization clock | I/O<br>CMOS | 1.8V         | Runtime         |         | Module Output if CPU acts in Master<br>Mode Module Input if CPU acts in<br>Slave Mode |

| AH18  | I2S0_SDOUT | S40   | I2S0 Digital audio Output                  | O CMOS      | 1.8V         | Runtime         |         |                                                                                       |

| AF18  | I2S0_SDIN  | S41   | I2S0 Digital audio Input                   | I CMOS      | 1.8V         | Runtime         |         |                                                                                       |

| AH19  | I280_CK    | S42   | I2S0 Digital audio clock                   | I/O<br>CMOS | 1.8V         | Runtime         |         | Module Output if CPU acts in Master<br>Mode Module Input if CPU acts in<br>Slave Mode |

| AJ17  | I2S2_LRCK  | S50   | I2S2 Left & Right<br>synchronization clock | I/O<br>CMOS | 1.8V         | Runtime         |         | Module Output if CPU acts in Master<br>Mode Module Input if CPU acts in<br>Slave Mode |

| AH16  | I2S2_SDOUT | S51   | I2S2 Digital audio Output                  | O CMOS      | 1.8V         | Runtime         |         |                                                                                       |

| AJ14  | I2S2_SDIN  | S52   | I2S2 Digital audio Input                   | I CMOS      | 1.8V         | Runtime         |         |                                                                                       |

| AH15  | I282_CK    | S53   | I2S2 Digital audio clock                   | I/O<br>CMOS | 1.8V         | Runtime         |         | Module Output if CPU acts in Master<br>Mode Module Input if CPU acts in<br>Slave Mode |

| AJ20  | AUDIO_MCK  | S38   | Master clock output to I2S co-<br>dec(s)   | O CMOS      | 1.8V         | Runtime         |         |                                                                                       |

# 4.3.4 USB 3.0 Ports

IMX8M Plus has integrated a USB Hub 3 and 2.0.

The following table shows the pins of the SMARC connector are used when the USB HUB feature is enabled.

| Ball # | Name           | Pin #      | Description                                                                | I/О Туре         | I/O<br>Level      | Power<br>Domain | PU /<br>PD | Comments                                                                                                                                                    |

|--------|----------------|------------|----------------------------------------------------------------------------|------------------|-------------------|-----------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | USB0+<br>USB0- | P60<br>P61 | USB differential data pairs for port 0                                     | I/O<br>USB       | USB               | Runtime         |            | Connected to USB HUB                                                                                                                                        |

| B5     | USB0_EN_OC#    | P62        | USB over-current sense<br>for port 0                                       | I/O OD<br>CMOS   | 3.3Vsb<br>/ 3.3V  | Runtime         | PU 10k     | Pulled low by Module OD<br>driver to disable USB0 power.<br>Pulled low by Carrier OD driver<br>to indicate over-current<br>situation.                       |

| A11    | USB0_VBUS_DET  | P63        | USB port 0 host power<br>detection, when this port is<br>used as a device. | I USB<br>VBUS 5V | USB<br>VBUS<br>5V | Runtime         |            | Can be connected to a USB client<br>port VBUS pin                                                                                                           |

| B11    | USB0_OTG_ID    | P64        | Input pin to announce<br>OTG device insertion on<br>USB 2.0 port           | I CMOS           | 3.3Vsb<br>/ 3.3V  | Runtime         |            |                                                                                                                                                             |

|        | USB1+<br>USB1- | P65<br>P66 | USB differential data pairs for port 1                                     | I/O USB          | USB               | Runtime         |            | Connected to USB HUB.                                                                                                                                       |

|        | USB1_EN_OC#    | P67        | USB over-current sense<br>for port 1                                       | I/O OD<br>CMOS   | 3.3Vsb /<br>3.3V  | Runtime         | PU 10k     | Connected to CPLD.<br>Pulled low by Module OD<br>driver to disable USB0 power.<br>Pulled low by Carrier OD driver<br>to indicate over-current<br>situation. |

|        | USB2+<br>USB2- | P69<br>P70 | USB differential data pairs for port 2                                     | I/O USB          | USB               | Runtime         |            | Connected to USB HUB                                                                                                                                        |

| Ball #     | Name                     | Pin #           | Description                                                                | I/О<br>Туре                                             | I/O Level                            | Power<br>Domain | PU /<br>PD | Comments                                                                                                                                                        |

|------------|--------------------------|-----------------|----------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------|-----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A9<br>B9   | USB2_SSRX+<br>USB2_SSRX- | S74<br>S75      | Receive signal differential<br>pairs for<br>SuperSpeed on port 2           | I<br>USB SS                                             | USB SS                               | Runtime         |            |                                                                                                                                                                 |

| A10<br>B10 | USB2_SSTX+<br>USB2_SSTX- | \$71<br>\$72    | Transmit signal differential<br>pairs for<br>SuperSpeed on port 2          | O<br>USB SS                                             | USB SS                               | Runtime         |            |                                                                                                                                                                 |

|            | USB2_EN_OC#              | P71             | USB over-current sense<br>for port 2                                       | I/O OD<br>CMOS                                          | 3.3Vsb /<br>3.3V                     | Runtime         | PU 10k     | <b>Connected to CPLD</b><br>Pulled low by Module OD driver<br>to disable USB0 power. Pulled<br>low by Carrier OD driver to<br>indicate over-current situation.  |

|            | USB3+<br>USB3-           | S68<br>S69      | USB differential data pairs for port 3                                     | I/O<br>USB                                              | USB                                  | Runtime         |            | Connected to USB HUB                                                                                                                                            |

| A12<br>B12 | USB3_SSRX+<br>USB3_SSRX- | S65<br>S66      | Receive signal differential<br>pairs for<br>SuperSpeed on port 3           | I<br>USB SS                                             | USB SS                               | Runtime         |            |                                                                                                                                                                 |

| A13<br>B13 | USB3_SSTX+<br>USB3_SSTX- | S62<br>S63      | Transmit signal differential<br>pairs for<br>SuperSpeed on port 3          | O<br>USB SS                                             | USB SS                               | Runtime         |            |                                                                                                                                                                 |

|            | USB3_EN_OC#              | P74             | USB over-current sense<br>for port 3                                       | I/O OD<br>CMOS                                          | 3.3Vsb /<br>3.3V                     | Runtime         | PU 10k     | <b>Connected to CPLD</b><br>Pulled low by Module OD driver to<br>disable USB0 power. Pulled low by<br>Carrier OD driver to indicate over-<br>current situation. |

|            | USB3_VBUS_DET            | <del>\$37</del> | USB port 3 host power<br>detection, when this port is<br>used as a device. | I<br><del>USB</del><br><del>VBUS</del><br><del>5V</del> | <del>USB</del><br><del>VBUS 5V</del> | Runtime         |            |                                                                                                                                                                 |

-

| USB3_OTG_ID | <del>S104</del> | Input pin to announce<br>OTG device insertion on<br>USB 3.0<br>port | <del>-I</del><br>- <del>CMOS</del> | <del>3.3Vsb /</del><br><del>3.3V</del> | Runtime |  |  |

|-------------|-----------------|---------------------------------------------------------------------|------------------------------------|----------------------------------------|---------|--|--|

|-------------|-----------------|---------------------------------------------------------------------|------------------------------------|----------------------------------------|---------|--|--|

| Ball # | Name                                 | Pin #                              | Description                               | I/О Туре                             | I/O<br>Level                               | Power<br>Domain    | PU / PD           | Comments                                                                                                                                              |

|--------|--------------------------------------|------------------------------------|-------------------------------------------|--------------------------------------|--------------------------------------------|--------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | USB4+<br>USB4-                       | S35<br>S36                         | USB differential data pairs for port 4    | I/O USB                              | USB                                        | Runtime            |                   | Connected to USB HUB                                                                                                                                  |

|        | USB4_EN_OC#                          | P76                                | USB over-current sense<br>for port 4      | I/O OD<br>CMOS                       | 3.3Vsb /<br>3.3V                           | Runtime            | PU 10k            | Connected to CPLD.<br>Pulled low by Module OD driver to disable<br>USB0 power. Pulled low by Carrier OD<br>driver to indicate over-current situation. |

|        | <del>USB5+</del><br><del>USB5-</del> | <del>\$59</del><br><del>\$60</del> | USB differential data pairs<br>for port 5 | <del>I/O USB</del>                   | <del>USB</del>                             | Standby            |                   |                                                                                                                                                       |

|        | USB5_EN_OC#                          | <del>\$55</del>                    | USB over current sense<br>for port 5      | <del>I/O OD</del><br><del>CMOS</del> | <del>-3.3Vsb</del><br>/<br><del>3.3V</del> | <del>Standby</del> | <del>PU-10k</del> | Pulled low by Module OD driver to<br>disable USB0 power. Pulled low by<br>Carrier OD driver to indicate over-<br>current situation.                   |

# 4.3.5 PCIe Port

IMX8M Plus the module supports one PCIe Gen 2.1 ports (PCIE\_A).

The following table shows the pins of the SMARC connector are used when the PCIe feature is enabled.

| Ball #     | Name                           | Pin #        | Description                                                                                   | I/О Туре                                | I/O<br>Level | Power<br>Domain | PU /<br>PD | Comments                                                                                         |

|------------|--------------------------------|--------------|-----------------------------------------------------------------------------------------------|-----------------------------------------|--------------|-----------------|------------|--------------------------------------------------------------------------------------------------|

| A15<br>B15 | PCIE_A_TX+<br>PCIE_A_TX-       | P89<br>P90   | Differential PCIe link A transmit data pair                                                   | O LVDS PCIE                             |              | Runtime         |            | Series AC coupled on module                                                                      |

| A14<br>B14 | PCIE_A_RX+<br>PCIE_A_RX-       | P86<br>P87   | Differential PCIe link A receive data pair                                                    | I LVDS PCIE                             |              | Runtime         |            | Series AC coupled off module                                                                     |

| D16<br>E16 | PCIE_A_REFCK+<br>PCIE_A_REFCK- | P83<br>P84   | Differential PCIe Link A reference<br>clock output                                            | O LVDS PCIE                             |              | Runtime         |            |                                                                                                  |

| AE16       | PCIE_A_RST#                    | P75          | PCIe Port A reset output                                                                      | O CMOS                                  | 3.3V         | Runtime         |            | Connected through Level Translator                                                               |

| AD14       | PCIE_WAKE#                     | S146         | PCIe wake up interrupt to host –<br>common to PCIe links A, B, C, D                           | I OD CMOS                               | 3.3V         | Runtime         | PU 10k     | Connected through Level Translator                                                               |

| A21<br>B21 | PCIE_D_TX+<br>PCIE_D_TX-       | \$29<br>\$30 | Differential PCIe link D transmit<br>data pair OR CSI0 differential input<br>(point to point) | I LVDS D-PHY<br>/ I LVDS M-<br>PHY,PCIE |              | Runtime         |            | this pin used for CSI0_D3_P &<br>CSI0_D3_N and added 0-ohm resistors<br>R299 & R300(made it DNP) |

| A22<br>B22 | PCIE_D_RX+<br>PCIE_D_RX-       | \$32<br>\$33 | Differential PCIe link A receive<br>data pair OR CSI0 differential input<br>(point to point)  | I LVDS D-PHY<br>/ I LVDS M-<br>PHY,PCIE |              | Runtime         |            | this pin used for CSI0_D2_P &<br>CSI0_D2_N and added 0-ohm resistors<br>R299 & R300(made it DNP) |

# 4.3.6 HDMI Port

IMX8M Plus the module supports one HDMI 2.0a ports (HDMI). The following table shows the pins of the SMARC connector are used when the HDMI feature is enabled

| Ball # | Name          | Pin # | Description                        | I/O<br>Type | I/O<br>Level | Power<br>Domain | PU /<br>PD | Comments |

|--------|---------------|-------|------------------------------------|-------------|--------------|-----------------|------------|----------|

| AH25   | HDMI_D0+      | P98   | HDMI Port, Differential Pair Data  | O TMDS      |              | Runtime         |            |          |

| AJ25   | HDMI_D0-      | P99   | Lines                              | HDMI        |              |                 |            |          |

| AH26   | HDMI_D1+      | P95   | HDMI Port, Differential Pair Data  | O TMDS      |              | Runtime         |            |          |

| AJ26   | HDMI_D1-      | P96   | Lines                              | HDMI        |              |                 |            |          |

| AH27   | HDMI_D2+      | P92   | HDMI Port, Differential Pair Data  | O TMDS      |              | Runtime         |            |          |

| AJ27   | HDMI_D2-      | P93   | Lines                              | HDMI        |              |                 |            |          |

| AH24   | HDMI_CK+      | P101  | HDMI Port, Differential Pair Clock | O TMDS      |              | Runtime         |            |          |

| AJ24   | HDMI_CK-      | P102  | Lines                              | HDMI        |              |                 |            |          |

| AC22   | HDMI_CTRL_CK  | P105  | I2C_CLK Line Dedicated to          | I/O OD      | 1.8V         | Runtime         | PU 100k    |          |

|        |               |       | HDMI                               | CMOS        |              |                 |            |          |

| AF22   | HDMI_CTRL_DAT | P106  | I2C_DAT Line Dedicated to          | I/O OD      | 1.8V         | Runtime         | PU 100k    |          |

|        |               |       | HDMI                               | CMOS        |              |                 |            |          |

| AE22   | HDMI_HPD      | P104  | HDMI Hot Plug Active High          | Ι           | 1.8V         | Runtime         | PU 100k    |          |

|        |               |       | Detection Signal that Serves as an | CMOS        |              |                 |            |          |

|        |               |       | Interrupt Request                  |             |              |                 |            |          |

# 4.3.7 LAN Port

IMX8M Plus the module supports two LAN ports is derived from the SOCs RGMII interface. The following table shows the pins of the SMARC connector that are used when the Ethernet feature is enabled.

#### Ethernet1:

| Ball #           | Name                                                                                                         | Pin #                                                | Description                                                                                                                                                                                                                                                                                                                                                       | <b>I/O</b><br>Туре | I/O<br>Level | Power<br>Domain | PU /<br>PD | Comments                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|-----------------|------------|-------------------------------------------------------------------------------------------|

| <br><br><br><br> | GBE0_MDI0+<br>GBE0_MDI0-<br>GBE0_MDI1+<br>GBE0_MDI1-<br>GBE0_MDI2+<br>GBE0_MDI2-<br>GBE0_MDI3+<br>GBE0_MDI3- | P30<br>P29<br>P27<br>P26<br>P24<br>P23<br>P20<br>P19 | Gigabit Ethernet Controller 0: Media Dependent Interface<br>Differential Pairs 0, 1, 2, 3. The MDI can operate in 1000,<br>100, and 10Mbit/sec modes.<br>Some pairs are unused in some modes according to the<br>following:<br><u>1000</u> 100 10<br>MDI[0]+/- B1_DA+/- TX+/- TX+/-<br>MDI[1]+/- B1_DB+/- RX+/- RX+/-<br>MDI[2]+/- B1_DC+/-<br>MDI[3]+/- B1_DD+/- | GBE<br>MDI         |              | Runtime         |            | Connected to<br>ETH-PHY.<br>Twisted pair<br>signals for<br>external<br>transformer.       |

|                  | GBE0_LINK100#                                                                                                | P21                                                  | Link Speed Indication LED for GBE 0 100Mbps                                                                                                                                                                                                                                                                                                                       | O OD<br>CMOS       | 3.3V         | Runtime         |            | Connected to ETH-<br>PHY.<br>Shall be able to sink<br>24mA or more<br>Carrier LED current |

|                  | GBE0_LINK1000#                                                                                               | P22                                                  | Link Speed Indication LED for GBE 0 1000Mbps                                                                                                                                                                                                                                                                                                                      | O OD<br>CMOS       | 3.3V         | Runtime         |            | Connected to ETH-<br>PHY.<br>Shall be able to sink<br>24mA or more<br>Carrier LED current |

| Ball # | Name           | Pin #          | Description                                                                                                | I/O<br>Type  | I/O<br>Level                | Power<br>Domain | PU /<br>PD | Comments                                                                                  |

|--------|----------------|----------------|------------------------------------------------------------------------------------------------------------|--------------|-----------------------------|-----------------|------------|-------------------------------------------------------------------------------------------|

|        | GBE0_LINK_ACT# | P25            | Link / Activity Indication LED Driven low on Link (10, 100 or 1000 Mbps) Blinks on Activity                | O OD<br>CMOS | 3.3V                        | Runtime         |            | <b>Connected to ETH-PHY.</b><br>Shall be able to sink 24mA or more<br>Carrier LED current |

|        | GBE0_CTREF     | <del>P28</del> | Center-Tap reference voltage for Carrier board<br>Ethernet magnetic (if required by the Module GBE<br>PHY) | Analog       | $\frac{0  to}{3.3V}$<br>max | Runtime         |            |                                                                                           |

|        | GBE0_SDP       | P6             | IEEE 1588 Trigger Signal. For hardware implementation of PTP (precision time protocol)                     | IO<br>CMOS   | 3.3V                        | Runtime         |            | Connected to Test point.                                                                  |

#### Ethernet2:

| Ball #                     | Name                                                                                           | Pin #                                                        | Description                                                                                                                                                                                                                                                                                                                                                       | I/О Туре     | I/O<br>Level | Power<br>Domain | PU /<br>PD | Comments                                                                                  |

|----------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|-----------------|------------|-------------------------------------------------------------------------------------------|

| -<br>-<br>-<br>-<br>-<br>- | GBE1_MDI0+<br>GBE1_MDI0-<br>GBE1_MDI1+<br>GBE1_MDI1-<br>GBE1_MDI2+<br>GBE1_MDI3+<br>GBE1_MDI3- | \$17<br>\$18<br>\$20<br>\$21<br>\$23<br>\$24<br>\$26<br>\$27 | Gigabit Ethernet Controller 1: Media Dependent Interface<br>Differential Pairs 0, 1, 2, 3. The MDI can operate in 1000,<br>100, and 10Mbit/sec modes.<br>Some pairs are unused in some modes according to the<br>following:<br><u>1000</u> 100 10<br>MDI[0]+/- B1_DA+/- TX+/- TX+/-<br>MDI[1]+/- B1_DB+/- RX+/- RX+/-<br>MDI[2]+/- B1_DC+/-<br>MDI[3]+/- B1_DD+/- | GBE<br>MDI   |              | Runtime         |            | <b>Connected to ETH-PHY.</b><br>Twisted pair signals for<br>external transformer.         |

|                            | GBE1_LINK100#                                                                                  | S19                                                          | Link Speed Indication LED for GBE 1 100Mbps                                                                                                                                                                                                                                                                                                                       | O OD<br>CMOS | 3.3V         | Runtime         |            | <b>Connected to ETH-PHY.</b><br>Shall be able to sink 24mA or<br>more Carrier LED current |

|                            | GBE1_LINK1000#                                                                                 | S22                                                          | Link Speed Indication LED for GBE 1 1000Mbps                                                                                                                                                                                                                                                                                                                      | O OD<br>CMOS | 3.3V         | Runtime         |            | <b>Connected to ETH-PHY.</b><br>Shall be able to sink 24mA or<br>more Carrier LED current |

| Ba | ıll # | Name           | Pin #           | Description                                                                                                | I/O Туре     | I/O<br>Level        | Power<br>Domain | PU /<br>PD | Comments                                                                                     |

|----|-------|----------------|-----------------|------------------------------------------------------------------------------------------------------------|--------------|---------------------|-----------------|------------|----------------------------------------------------------------------------------------------|

|    | -     | GBE1_LINK_ACT# | S31             | Link / Activity Indication LED Driven low on Link (10, 100 or 1000 Mbps) Blinks on Activity                | O OD<br>CMOS | 3.3V                | Runtime         |            | <b>Connected to ETH-PHY.</b><br>Shall be able to sink 24mA<br>or more Carrier LED<br>current |

|    |       | GBE1_CTREF     | <del>\$28</del> | Center-Tap reference voltage for Carrier board<br>Ethernet magnetic (if required by the Module GBE<br>PHY) | Analog       | 0 to<br>3.3∨<br>max | Runtime         |            |                                                                                              |

|    |       | GBE1_SDP       | P5              | IEEE 1588 Trigger Signal. For hardware implementation of PTP (precision time protocol)                     | IO CMOS      | 3.3V                | Runtime         |            | Connected to Test point.                                                                     |

# 4.3.8 SDIO Port

IMX8M Plus the module supports one MMC/SD/SDIO port. The port is derived from the i.MX8M Plus on-chip MMC/SD/SDIO controller (uSDHC2). The following table shows the pins of the SMARC connector are used when the SDIO feature is enabled.

| Ball #                       | Name                                     | Pin #                    | Description                                                                                                                                                                                                                  | I/О Туре     | I/O                      | Power             | PU/    | Comments                                                                                                                                        |

|------------------------------|------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------|-------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|